Реферат: Разработка схемы электронного эквалайзера

Реферат: Разработка схемы электронного эквалайзера

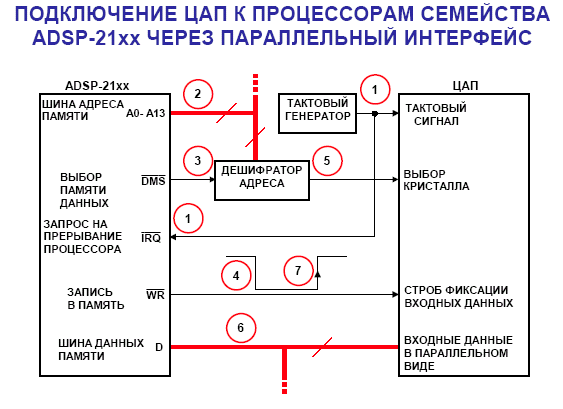

Рис.14.

Таким образом, процесс записи инициируется периферийным устройством посредством установления сигнала запроса прерывания DSP-процессора, указывающего, что периферийное устройство готово к приему новых данных (шаг N 1). Далее DSP-процессор выставляет адрес периферийного устройства на адресной шине (шаг N 2) и переводит в активное состояние сигнал выбора памяти DMS (шаг N 3). Это приводит к тому, что дешифратор адреса выдает сигнал выбора (chip select) на периферийное устройство (шаг N 5). После спадающего (переднего) фронта сигнала DMS через промежуток времени tASW процессор переводит в активное нулевое состояние сигнал записи WR (шаг N 4). Длительность импульса WR составляет tWP нс. Данные помещаются на шину данных (D) и удерживаются в течение времени tDW, до перехода сигнала WR в неактивное единичное состояние (шаг N 6). Восходящий (задний) фронт сигнала WR используется для фиксации присутствующих на шине данных (D) во внешнюю параллельную память (шаг N 7). Данные на шине остаются достоверными еще в течение времени tDH после прохождения положительного фронта сигнала WR.

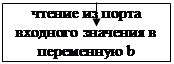

Основные требования по временным параметрам при записи данных в периферийное устройство показаны на рис. 14. Главным параметром здесь является длительность строба записи tWP. Для всех периферийных устройств, кроме самых быстрых, придется использовать циклы ожидания, т.к. этим устройствам нужно больше времени для доступа к данным.

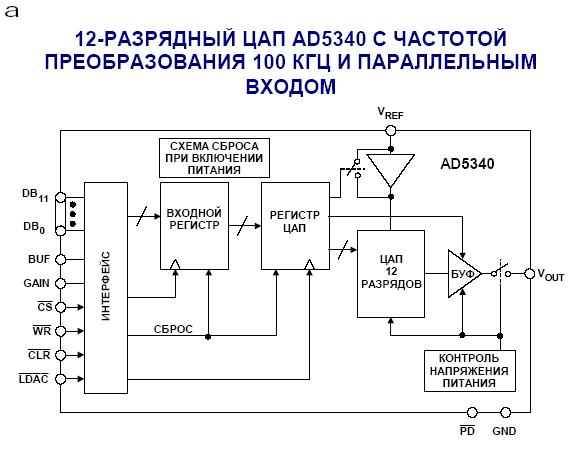

Микросхема AD5340 – это 12-ти разрядный ЦАП, работающий на частоте дискретизации 100 кГц, имеющий параллельный цифровой интерфейс. Данный АЦП питается от однополярного источника питания напряжением +2.5-5.5 В и рассеивает мощность 345 мкВт (при напряжении питания 3 В). В энергосберегающем режиме потребляемая мощность прибора снижается до 0.24 мкВт. ЦАП AD5340 имеет в своем составе выходной буферный усилитель, который способен формировать выходной сигнал в диапазоне значений от нуля до напряжения питания. В ИС AD5340 можно задействовать или отключить встроенный буфер для источника опорного напряжения. В устройстве имеется встроенная схема формирования сигнала сброса при включении питания, гарантирующая нулевое значение сигнала на выходе ЦАП до тех пор, пока в ЦАП не будут записаны корректные данные. Структурная схема ЦАП показана на рис. 15. На входе прибора осуществляется двойная буферизация данных. Спецификация временных параметров цикла записи для ADSP-2189M дается для тактовой частоты 75 МГц.

Рис.15.

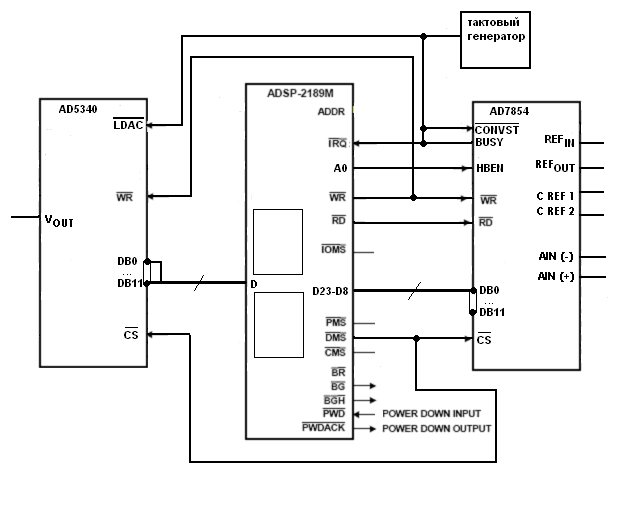

Исследование временных характеристик, изображенных на рис. 7.14, показывает, что для обеспечения совместимости по синхронизации между устройствами потребуется программирование двух циклов ожидания в процессоре ADSP-2189M. Это позволяет увеличить длительность строба записи (WR) до 30.25 нс, что превышает минимально необходимую длительность строба записи в ЦАП AD5340 (20 нс). Минимальное время установления данных в микросхеме AD5340, равное 5 нс, также перекрывается при использовании двух циклов ожидания. Схема интерфейса между двумя устройствами показана на рис. 16.

Параллельные интерфейсы с другими DSP-процессорами могут быть организованы подобным образом, для чего необходимо подробное изучение временных спецификаций всех соответствующих сигналов каждого из взаимодействующих устройств.

Рис.16.

Рис. 17. Принципиальная схема DSP системы.

Алгоритм работы устройства ADSP-21XX

|

+1+2NПФ3+1+2NПФ4+1}

{ai, xi – массив, i=1,2..М}

![]()

![]()

|

|||||||

![]()

![]()

![]()

Программа и графики АЧХ фильтров

program k(t);

uses crt,graph;

label 1,2,3;

const f1=1000;

const f2=520;

const fd=20000;

var A,Re,Mn,Td,w1,w2,w,wt,wtp:real;

n,x,y:integer;

Road:STRING;

f:text;

kt:array[0..105] of real;

begin

clrscr;

writeln ('File name?');

readln (road);

assign (f, Road);

rewrite(f);

writeln(f,' w',' ',' A');

w1:=2*pi*f1;

w2:=2*pi*f2;

Td:=1/fd;

n:=0;

w:=0;

x:=detect;

InitGraph(x,y,'c:\tp7\tp7\bgi');

line(0,479,640,479);

line(0,0,0,479);

repeat

wt:=2*pi*w/20000;

re:=0;

mn:=0;

n:=0;

repeat

if n=0 then goto 1 else goto 2;

2:kt[n]:=(sin(w1*n*Td)-sin(w2*n*Td))/(pi*n*Td);

goto 3;

1:kt[n]:=(w1-w2)/pi;

3:re:=re+kt[n]*cos(wt*n);

mn:=mn+kt[n]*sin(wt*n);

if n=0 then mn:=0;

n:=n+1;

until n>81;

A:=sqrt(sqr(re)+sqr(mn));

writeln (f,' ',w:5:2,' ',A:5:4);

x:=trunc(w/46.88);

putpixel(x,trunc(-A/41.67+480),7);

if w=620 then begin

y:=trunc(-A/41.67+480);

repeat

line(trunc(w/46.88),y,trunc(w/46.88),y+5);

y:=y+20;

until y>479;

end;

if w=1000 then begin

y:=trunc(-A/41.67+480);

repeat

line(trunc(w/46.88),y,trunc(w/46.88),y+5);

y:=y+20;

until y>479;

end;

w:=w+1;

until w>=20000;

close(f);

repeat until keypressed;

end.

Вывод.

В курсовой работе был успешно разработан эквалайзер, применяемый в микропроцессорной технике в системах передачи информации.

В качестве базового был использован в качестве сигнальный процессор семейства ADSP-21xx фирмы ANALOG DEVICES. Процессоры этой фирмы являются оптимальными по соотношению цены к качеству и нашли широкое применение в современных системах цифровой обработки сигналов.

Литература

1.Методические указания и задания на курсовой проект « Разработка эквалайзера »

2. Курс лекций по дисциплине « МИУСС » -