Курсовая работа: Вычислитель аналогового сигнала

Курсовая работа: Вычислитель аналогового сигнала

На вход CLC АЦП поступает тактовая частота, получаемая с процессора. Происходит запуск подпрограммы обработки прерывания. Подпрограмма осуществляет проверку готовности данных АЦП по сигналу готовности преобразования (выход ГТ), который поступает на вход "HSI.0" блока HSIO. Если данные готовы, то по сигналу RDA (сигнал RD, разрешенный сигналом SEL0) происходит чтения с шины данных преобразованного значения, выставляется адрес следующего аналогового входа, и запускается программируемый таймер, который через несколько тактов обращается к порту запуска АЦП, разрешая тем самым преобразование входного сигнала. Процесс повторяется. Выходной регистр АЦП выдает преобразованный код на шину данных только по сигналу "RD" микроконтроллера.

При необходимости выборки и преобразования сигнала с максимальной заданной частотой со всех аналоговых входов микроконтроллер вынужден обращаться к АЦП через:

t=1/(2*fmax)=1/(2*100)=5 мкс;

где t-период обращения, рассчитывается по теореме Котельникова.

fмах=200кГц; - максимальная частота сигнала;

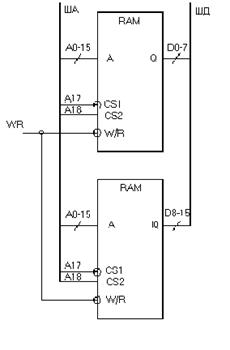

Работа микроконтроллера с внешней ОЗУ (рис.6) осуществляется с помощью встроенного контроллера внешней памяти, выставляющего сигналы записи WR, сигналы А17, А18 и сигнал ALE наличия на шине адреса/данных сигналов адреса.

Рисунок 6. Внешнее ОЗУ.

Обмен информацией между микроконтроллером и ОЗУ идет по шине адреса/данных частями, по машинному слову в 16 бит. При формировании адреса сигналы адреса фиксируются в регистре адреса и подаются на адресные входы микросхем ОЗУ. Чтение и запись данных в ОЗУ производится по одним и тем же выводам. Запись сопровождается подачей на соответствующий вход ОЗУ сигнала "WR", а его неактивное состояние подготавливает ОЗУ для считывания. Код адреса по сигналу ALE сохраняется в специальных регистрах, которые удерживают его на входах ОЗУ в то время, когда на совмещенной шине адреса/данных выставлены данные. ОЗУ активизируется только тогда, когда на шину выставляется адрес, содержащий в старшем, А17 разряде слова адреса "1" (выбора кристалла CS2) и в А18 (А19) разряде слова адреса "0". При установление иных значений А17 и А18 обмен с ОЗУ запрещается, тем самым предотвращая конфликты с дешифратором адреса. Карта распределения адресного пространства проектируемого устройства представлена в таблице 1.

Таблица 1. Карта распределения адресного пространства.

|

07FFFFH 040000H |

Память данных 128кбайт |

|

00FFFFH 00C000H |

Не используется |

|

00B002H 00B001H 00B000H |

Чтение цифровых входов Запуск АЦП Чтение АЦП |

|

00AFFFH 00A000H |

Порты индикатора |

|

009FFFH 002000H |

Внутреннее ПЗУ 32кбайт |

|

001FFFH 001F00H |

Внутренние спецрегистры |

|

001EFFH 000600H |

Не используется |

|

0003FFH 000100H |

Внутреннее ОЗУ |

|

0000FFH 000018H |

Регистровое ОЗУ |

|

000017H 000000H |

Спецрегистры процессора |

2.1.3 Принципиальная схема

Аналоговые сигналы поступают через разъем XS1 и резисторы R1, R5 на выводы 2 операционных усилителей DA1…DA2. Операционные усилители усиливают сигналы приблизительно в 10 раз, после чего они поступают на входы D аналогового коммутатора DD2. В зависимости от того, какой адрес выставлен на адресном входе А0..А3, один из 2 сигналов поступает на его выход Q (в.32 DD4). Резисторы R1…R4, R5…R8 предназначены для установки коэффициента усиления операционных усилителей. Резисторы R1…R6 служат для балансировки операционных усилителей.

Сигнал, поступающий на вход IN АЦП (в.15 DA3) преобразовывается в цифровой код. Преобразование происходит при поступлении импульсов на вход CLC от процессора DD4. После окончания преобразования на выходе RAD (в.7 DA3) появляется логическая "1", поступающая на вход SCO процессора. С выходов D0…D11 АЦП цифровой код поступает на регистры "защелки" выполненных на микросхемах DD5, DD6. Регистры записывают и содержат достоверную информацию при наличии на входах CLK и EZ (в.11, 1 DD5, DD6) сигнала RDA. Сигнал RDA формируется логическим сложением микросхемой DD1.2 сигналов RD (чтение процессором из внешнего источника) и SELO (выбор порта). Все остальное время выходы регистров находятся в третьем состоянии для устранения искажений информации. С выходов регистров информация поступает на входы AD для обработки и хранения в ОЗУ. Номер канала устанавливается циклически по сигналу чтения АЦП путем подачи на вход счетчика DD3. Разрешение записи в регистр осуществляется сигналом SELO и происходит во время действия сигнала чтения АЦП.

Накапливаемая контроллером информация хранится в шестнадцатиразрядном ОЗУ, организованной в две "страницы" объемом по 128 Кбайт. Обмен с ОЗУ производится за два шинных цикла. Во время первого цикла на выводы AD0…АD15 процессора DD4 выставляется адрес, который фиксируется в регистрах адреса выполненных на микросхемах DD7, DD8. Фиксация адреса происходит при выставлении процессором сигнала на выходе ALE, который подается на входы CLK микросхемы регистров адреса (в.11 DD9, DD10). После снятия сигнала CLK на выходах Z регистров остается адрес в ОЗУ, который подается на адресные входы микросхем памяти DD10, DD11. Во время второго цикла процессор выставляет сигнал WR, поступающий на входы W/R микросхем ОЗУ (в.29 DD10, DD11), на выводы AD0…АD15 информацию, которая подается на выводы DIO и производит запись информации в ОЗУ. Если сигнал WR не выставляется процессором, ОЗУ находится в режиме "чтение" и процессор может считывать данные, поступающие на выводы AD0…AD15. Сигналы с выводов А17…А19 так же подаются на входы ОЗУ CS2 и CS1 (DD3, DD7) и CS1 (DD8, DD14) соответственно. При наличии логической "1" на линии А17 и логического "0" на линии А18 разрешается чтение или запись в первую "страницу" памяти (DD3, DD7). При наличии логической "1" на линии А17 и логического "0" на линии А19 разрешается запись или чтение во вторую "страницу" памяти (DD8, DD14). При наличии логического "0" на линии А17, ОЗУ блокируется и производится запись адреса в дешифратор адреса DD2.

Дешифратор адреса собран на микросхемах DD2, DD1.1 и DD1.2. Сигналы с выходов процессора А17…А19 поступают на выводы 1, 2 DD1.1 и вывод 5 DD1.2 соответственно. При наличии на этих выводах логического "0", на выводе 6 DD1.2 появляется строб импульс обращения к порту, подающий на вход CS микросхемы DD2. На линиях AD0…AD15 процессор выставляет адрес порта, который подается на адресные входы DD2. На выходах D0 микросхемы DD4 появляется управляющий сигнал SEL0…3, соответствующий выбранному порту.

Индикатор собран на семисегментных индикаторах 2х6. Процессор выставляет адрес на линиях АD0-4, записывает его в регистр адреса. При обращении процессора к порту индикатора DD2 выставляет на выводе 17 сигнал SEL1. Параллельно сигналы с линий AD0-15 записываются как отображаемая информация в регистры DD13 и DD14. Запись производится при наличии на входах CLK регистров сигнала SEL1. Одновременно по сигналу SEL1 адрес из регистра адреса поступает на дешифратор DD12, который, дешифруя поступившую на вход информацию, выбирает необходимый столбец для отображения информации. Информация из регистров DD13 и DD14 подается на индикаторы, включение которого происходит от дешифратора.