Курсовая работа: Вычислитель аналогового сигнала

Курсовая работа: Вычислитель аналогового сигнала

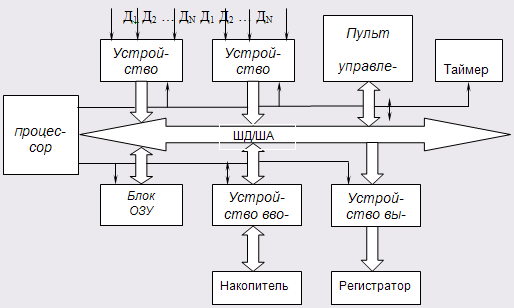

Таймер синхронизирует работу всей системы, и его сигналы могут служить метками реального времени.

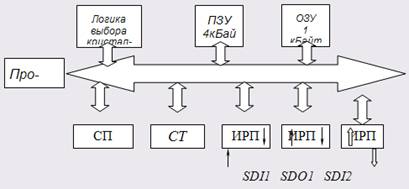

В качестве второго примера была выбрана схема одноплатного микроконтроллера мМС1204 [2], которая приведена согласно рисунку 2.

Рисунок 1 - Структурная схема АСК централизованного типа.

Базовой моделью семейства является микроконтроллер мМС1200 [3], который представляет собой законченную одноплатную МС общего назначения с магистрально-модульной архитектурой открытого типа. Основой МС служит шина И41 [3]. На плате отсутствуют какие-либо средства для реализации специальных функций, ориентированных на конкретные применения. Специфичность и разнородность таких средств привели бы к перегрузке платы и ее не эффективному использованию. Поэтому основное внимание было уделено интегрированию действительно универсального базового набора программно-аппаратных средств, обладающего функциональной завершенностью и обеспечивающего применение микроконтроллера в качестве ядра информационных систем.

Рисунок 2 - Схема одноплатного микроконтроллера мМС1204

В состав микроконтроллера входят: 8-разрядный процессор, ПЗУ, ОЗУ, два последовательных интерфейса типа ИРПС и параллельный интерфейс типа ИРПР. Системный таймер (СТ) совместно с 8-уровневой системой прерываний (СП) обеспечивает поддержку режима реального времени, который характерен для многих применений микроконтроллера. Внутрисистемная магистраль организует многоплатные расширения микроконтроллера с помощью специальных и системных модулей, таких как модуль аналогового ввода или системная память соответственно.

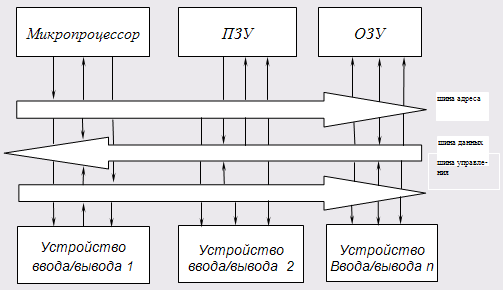

В [1] найдена структурная схема вычислителя на базе заданного процессора поясняющая принцип действия микроЭВМ, которая представлена согласно рисунку 3.

Схема включает следующие узлы:

-микропроцессор;

-блоки ПЗУ и ОЗУ;

-блоки устройств ввода/вывода.

Микропроцессор выставляет на шину адреса (ША) адрес того блока, к которому необходимо обратиться во время той или иной фазы. Вместе с этим на шину управления (ШУ) выставляется управляющий код, необходимый для настройки блока по выставленному адресу. Например, для задания режима чтения ОЗУ необходимо на шину адреса выставить адрес необходимой ячейки ОЗУ, а на шину управления подать сигнал RD.

Рисунок 3

По шине данных (ШД) происходит обмен данных между микропроцессором и блоками вычислителя. Данные пересылаются после установки адреса на шине адреса и сигналов управления на шине управления.

Количество устройств ввода-вывода в вычислителе может быть различным. Их присутствие в микроЭВМ обязательно, так как при их отсутствии отпадает необходимость в самом вычислителе. Для обмена информацией между микроЭВМ и устройствами ввода-вывода также необходимо адресовываться к ним и посылать управляющие коды по шинам.

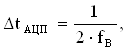

Ввод сигнала, его представление в дискретную форму, проводится с учетом требуемого интервала дискретизации, определяемого теоремой Котельникова, согласно формуле (1). Величина Dt определяет временной интервал только для одного сигнала.

(1)

(1)

где fB - верхняя гармоника сигнала, Гц

![]() (2)

(2)

где f0 - частота сигнала, Гц

![]()

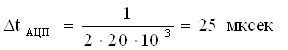

Быстродействие АЦП составит 25 мкс. Разрядность АЦП определим исходя из погрешности представления информации dПР

![]() (3)

(3)

![]()

Определим число разрядов АЦП исходя из формулы (4)

![]() (4)

(4)

где n - число разрядов

![]()

Тогда

Выбираем АЦП с разрядностью n=12 и частотой f ³ МГц.

Выбираем АЦП AD 1671 по [9], у которого n=12, f= МГц.

Расчет ОЗУ произведем следующим образом

(5)

(5)

где m - количество каналов;

Dt - временной интервал накопления, с

Dt зададимся 0,1 с., тогда количество измерений на интервале будет состовлять 0,1/25 10 -6=4000.

![]()

Таким образом, ОЗУ составит 128 КБайт. Выбираем микросхему

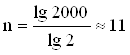

В соответствии с техническим заданием информационно-вычислительная система обработки сигналов должно состоять из следующих устройств: микроконтроллер, ПЗУ, ОЗУ. Клавиатура - 12 функциональных клавиш, устройство ввода аналогового сигнала (подсистема ввода сигнала), LPT-порт и семисегментная индикация, состоящего из 6 столбцов, 2 строк.

Устройство ввода аналогового сигнала имеет два входа, где аналоговый сигнал преобразуется в цифровой код, выставляется на шину данных. Далее эти данные записываются в ячейку памяти ОЗУ для накопления и хранения информации. Сигналы шины адреса фиксируется в регистре адреса. После обработки информации выводится на информационное табло собранное на семисегментных индикаторах.

ПЗУ предназначено для хранения команд программы.

Оперативное управление работой системы осуществляется с клавиатуры.

3. Техническое проектирование

3.1 Разработка принципиальной схемы

3.1.1 Структурная схема устройства

Структурная схема представлена на рисунке 1.

Рисунок 1. Схема структурная.

Устройство содержит процессорный блок, к встроенным портам которого подключен порт клавиатуры. Через совмещенную шину адреса/данных подключается АЦП - имеющий 2 аналоговых входа, внешнее ОЗУ и блок отображения информации. Сигналы шины адреса фиксируются в регистрах адреса по сигналу ALE.

АЦП управляется специальными сигналами микроконтроллера, ОЗУ – встроенным в микроконтроллер блоком управления внешней памяти, блок отображения – непосредственно сигналами с шины адреса и шины данных.

3.1.2 Функциональная схема устройства

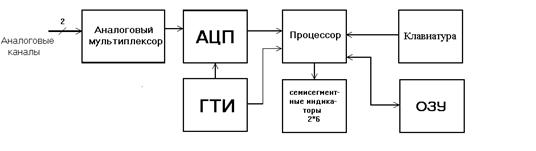

Процессорный блок (Рисунок 2) обеспечивает преобразование полученной информации, управление режимами работы периферийных устройств, инициализацию всего устройства по включении питания.

Основным устройством этого блока является микроконтроллер. Он включает в себя 20-битный центральный процессор, который соединен с контроллером прерываний и с контроллером памяти через 16-битную внутреннюю шину CPU. Расширение этой шины соединяет CPU со встроенными периферийными модулями Дополнительно: по 8-битной шине CPU передаются командные биты от контроллера памяти к регистру команд в регистровом арифметическом устройстве. Тактовую частоту микроконтроллера задает внешняя генерирующая цепочка с кварцевой стабилизацией. Она подключается к его входам XTAL1 и XTAL2. Сброс устройства осуществляется подачей низкого уровня напряжения на вход "RESET". Используемыми при построении системы сбора информации встроенными периферийными модулями микроконтроллера являются: один однонаправленный (вывод) и два двунаправленных восьмиразрядных порта ввода/вывода, программируемый таймер, модуль высокоскоростного ввода/вывода (HSIO), встроенное ПЗУ на 32Кбайт.

Рисунок 2. Процессорный блок.

Два порта ввода/вывода используются в качестве мультиплексированной 16-разрядной шины адреса/данных (сигналы AD0-AD15), которые сами настраиваются на этот режим при включении питания.

Для формирования сигнала адреса для ОЗУ и внешних устройств используется регистр адреса, запись в который происходит при активном уровне сигнала ALE. Блок клавиатуры подключается через встроенные порта ввода-вывода процессора.

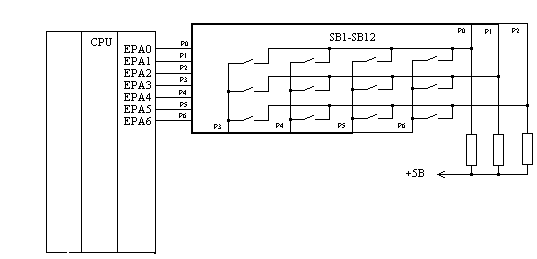

Рисунок 3. Подключение клавиатуры.

Данные с них считываются при обращении вычислителя к порту.

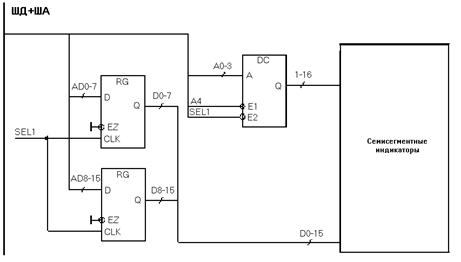

Блок отображения информации (Рисунок 4) осуществляет вывод данных на семисегментные индикаторы, состоящие из 2 строк и 6 столбцов.

Рисунок 4. Блок отображения информации.

Отображение производится следующим образом: при обращении к соответствующему порту, ПЛМ преобразует поступившую с регистра адреса информацию в сигнал управления SEL1, переводит в активное состояние регистры данных и тем самым разрешает включение разрядов отображаемого символа на индикаторах. Одновременно код с регистров адреса поступает на входы дешифраторов, работа которых также разрешается сигналом SEL1. Запись в дешифраторы осуществляется за два цикла обмена, в зависимости от состояния линии А4 включается дешифратор. В зависимости от поступившего адреса дешифраторы включают тот или иной индикатор.

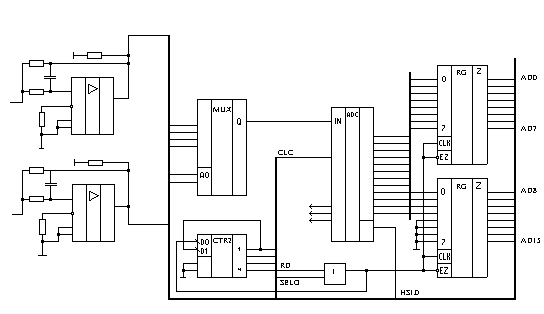

При работе с АЦП (Рисунок 5) микроконтроллер переходит на адрес 030000, по которому в адресном пространстве системы подразумевается 16-битная ячейка памяти, предназначенная для хранения преобразованного цифрового кода одного из входов АЦП.

Рисунок 5. Блок ввода аналоговой информации.

Сигналы адреса поступают на вход ПЛМ, которая отслеживает соответствие его диапазону адресов, выделенных для АЦП, и преобразует сигналы шины адреса в сигнал SEL0, управляющий счетчиком с одновременным чтением состояния АЦП, передающим адрес аналоговому мультиплексору. Аналоговый сигнал проходит через соответствующую схему коррекции, которая согласовывает уровень и форму входящего сигнала так, чтобы он имел наименьшие искажения, на вход АЦП.