Реферат: Схема микропроцессора

Реферат: Схема микропроцессора

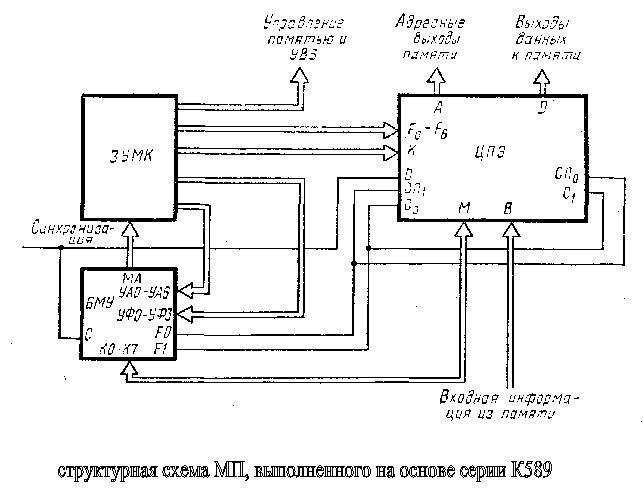

На рис 3 показана структурная схема такого процессора. Микропрограмма, находящаяся в управляющей памяти, после выключения питания устанавливает ЦП в исходное состояние и осуществляет выборку и выполнение команд. Разрядность слова микропрограммной памяти определяется числом и разрядностью микроинструкций.

Центральный процессорный элемент имеет шесть групп входов и выходов, по которым происходит связь с другими схемами. Четыре из них (В, М, А, D) используются преимущественно для связи с внешней памятью и устройствами ввода – вывода. Группа выводов F0 – F6 используется для управления работой ЦПЭ, а входы К – для маскирования информации для занесения константы.

Блок микропрограммного управления. Он имеет восемь входов команды К (макрокоманды). Таким образом, информация о коде операции определяется восемью разрядами, т. е. максимальное число макрокоманд 256. Число разрядов микрокоманды, требуемое для управления БМУ, равно: семь разрядов УАО – УА6 – для управления выработкой перехода к следующему адресу микрокоманды и четыре УФ0 – УФ3 – для управления схемой выработки признаков условных переходов. Таким образом, для управления ЦПЭ и БМУ необходимо 19 разрядов. Кроме этих микроинструкций необходимы дополнительные микроинструкции для управления памятью, вводом – выводом и т. д.

Данные в АЛУ поступают из памяти из устройства ввода информации и одаются в регистр-аккумулятор. В него поступают также результаты операций, выполняемых в АЛУ. После завершения операций данные посылаются в память или в устройства вывода информации.

Устройство управления управляет операциями в соответствии с содержанием команд, которые считываются из внешнего ЗУ, и помещаются в регистр команд. Адрес очередной команды обычно определяется счетчиком команд. В качестве регистра и счетчика команд используются внутренние регистры ЦПЭ.

Связь с ЗУ осуществляется через регистр адреса памяти и регистр данных памяти, выходы которых соединены с соответствующими адресными и информационными сигналами. Разрядность адреса памяти определяет адресуемое поле памяти. Часть регистров МП используется в качестве сверхоперативной памяти, в которой хранятся промежуточные результаты вычислений. Это позволяет повысить быстродействие процессора.

Для обеспечения контроля за состоянием регистров при выполнении операций используются регистры состояний блока микропрограммного управления (БМУ). Триггеры этих регистров (флажки) индицируют переполнение регистров ЦПЭ, нулевое содержание аккумуляторов, знак его содержимого и другие состояния. Эта информация используется для организации условных переходов в микропрограммах.

Синхронизация работы отдельных узлов процессора осуществляется одной или несколькими сериями тактовых импульсов. Для реализации одной команды необходимо несколько периодов тактовых импульсов. Командный цикл состоит из цикла выборки, во время которого вырабатывается адрес команды и по нему вырабатывается команда и считываются в регистр данные из памяти, и цикла , исполнительного, во время которого в устройстве управления команда дешифруется и процессор исполняет ее.

Рассмотрим подробно структуру и основные характеристики отдельных БИС комплекта серии К589.

Центральный процессорный элемент предназначен для логической и арифметической обработки информации, приема, хранения и выдачи оперативной информации, а также для формирования адресов памяти. Он представляет собой двухразрядную микропроцессорную секцию со структурой, обеспечивающей практически неограниченные возможности объединения кристаллов ЦПЭ по горизонтали с целью увеличения разрядности процессора.

Основная особенность ЦПЭ – большое число шин: три входные и две выходные с адресным регистром данных это обеспечивает возможность выдачи данных и адресов в память одновременно. Назначение шин ЦПЭ – пересылка байтов, тестирование битов, ввод – вывод информации во внутренние регистры.

Формирователи выходных шин выполнены на элементах с тремя состояниями, что существенно упрощает подключение УПЭ к магистрали. Шина микрофункций управляет работой секций, выбирая операнды и операции, которые должны выполнятся в АЛУ. ЦПЭ выполняет свыше 40 логических и арифметических операций. Секция выдает сигналы ускоренного переносы. Кроме того, она снабжена независимыми линиями входа и выхода переноса, входа и выхода сдвигаемого кода.

В состав ЦПЭ входят АЛУ, 11 сверхоперативных регистров, два мультиплексора (А и В), аккумулятор, регистр адреса памяти, дешифратор микрофункций.

Информация на ЦПЭ поступает по трем группам независимых входов М, В и К из основной памяти, устройств ввода – вывода, памяти микропрограмм. Информация, поступающая на ЦПЭ, хранится в 11 регистрах R0 – R9 , T , а также в накапливающем регистре АС или в регистре адреса памяти. Через мультиплексоры А и В информация передается в АЛУ. Регистры R0 - R9 и Т выполняют функции сверхоперативного запоминающего устройства и могут быть использованы как счетчики. Информация с регистров через мультиплексор А поступает в АЛУ, а с выхода АЛУ – снова на регистры. Аккумулятор служит для хранения результата операций АЛУ. Информация с выхода аккумулятора поступает на вход АЛУ или через выходной усилитель – буфер – может выдаваться на выходную магистраль для передачи в основную память или на устройство ввода – вывода. Через мультиплексоры А и В она может подаваться на один из двух входов АЛУ. На входы мультиплексора А поступают данные со входов М, регистров R0 – R9 , Т и аккумулятора, а на входы мультиплексора В – информация со входов В , К и аккумулятора. При этом производится маскирование информации входов В и АС данными на входах К. результат операций, выполняемых в АЛУ, может хранится в R0 – R9 и аккумуляторе.

При операции сдвига в право используют вход СП1 и выход СП0, для организации последовательного переноса - вход С1 и выход С0. Наличие выходов Х и У обеспечивает организацию ускоренного (сквозного) переноса между микросхемами ЦПЭ. При неарифметических операциях схемы переноса используют для выполнения логического ИЛИ всех разрядов слова с учетом маскирования по входам К. Входом К пользуются при арифметических операциях для маскирования полей и отдельных разрядов обрабатываемых слов. Через входы К в ЦПЭ могу подаваться константы из памяти микропрограмм. Обычно регистр адреса используется для хранения и пересылки адреса команд в основную память. В этом случае информация с АЛУ через отдельный выход поступает на регистр памяти. В каждом микрокомандном цикле на входы F поступает микроинструкция (часть поля микрокоманды,), которая дешифруется и определяет выполнение необходимы операций ЦПЭ. Микроинструкция F0-F6 разбита на два поля F и R- группы. F -группы (F4-F0) определяет код операции, регистровая R- группа (F0-F3) - адрес регистров.

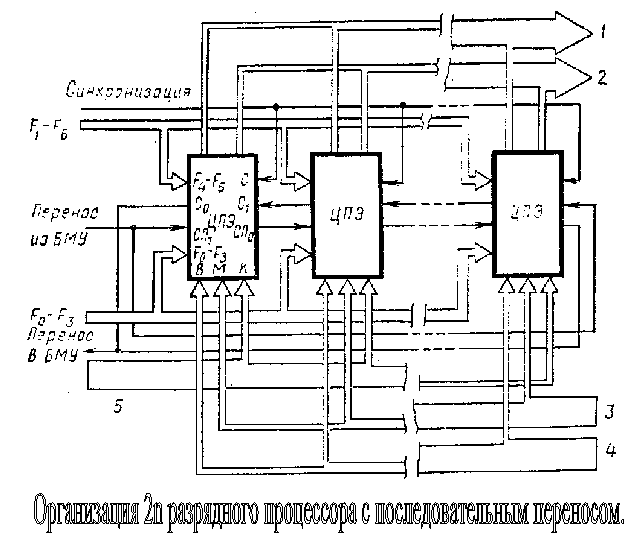

На рис. 4 показан вариант соединения БИС ЦПЭ с последовательным переносом, осуществляемым с помощью БИС ускоренного переноса. Цикл обработки ЦПЭ составляет 100 нс.

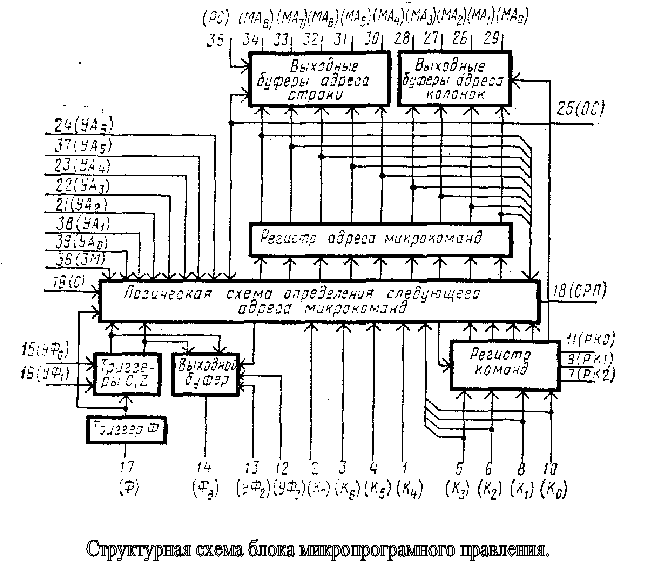

Блок микропрограммного управления предназначен для управления последовательностью выборки микрокоманд из управляющей памяти (ЗУМК) и выполняет следующие функции: управление регистром адреса микрокоманды; выборку очередной микрокоманды с учетом содержимого РАМК; хранение и выдачу признаков; управление микропрограммными прерываниями. В состав БМУ (рис. 5) входят: девятиразрядный регистр адреса микрокоманд и соответствующая магистраль; схема формирования очередного адреса; выходные буферы адреса микрокоманды на элементах с тремя состояниями; триггеры признаков (C, Z, Ф); регистр команды; выходной буфер флажков.

Формирование адреса очередной микрокоманды выполняется с помощью условных и безусловных переходов. В каждой текущей микрокоманде содержится поле микроинструкции БМУ, предназначенной для формирования адреса следующей микрокоманды. Адреса микрокоманды (всего 512) образуют матрицу (страницу), состоящую из 32 строк и 16 столбцов. Каждый адрес определяется номером той строки и того столбца, на пересечении которых он находится. Под адрес строки отводится пять разрядов (МА8 – МА4), а под адрес столбца четыре разряда (МА3 – МА0). Девятиразрядный адрес микрокоманды, выработанный логикой следующего адреса, загружается в регистр адреса микрокоманд, а из него выдается в память микрокоманд по десяти выходным шинам.

Блок микропрограммного управления обеспечивает хранение текущего значения на выходе переноса ЦПЭ (С0, СП0) и управляет информацией на входе переноса (С1, СП1). С помощью двух групп микроинструкций осуществляется управление признаками - установка и их выдача. Схема обработки признаков содержит три триггера: С и Z и триггер - защелку Ф, в которой запоминается текущее состояние выхода переноса ЦПЭ. Логическая схема признаков совместно со схемой переноса ЦПЭ используется для выполнения арифметических и сдвиговых операций.

Сигнал в двоичном коде на входах УА используется для формирования адресов строки и столбца и вида микроопераций, выполняемой БМУ. По четырем микроинструкциям производятся безусловные переходы, по остальным - условные. Для формирования адреса следующей микрокоманды при безусловных переходах используется адрес текущей микрокоманды, который хранится в регистре адреса и ряд битов микроинструкции УА0-УА6: при условных переходах - адрес текущей (предыдущей) микрокоманды и содержимое регистров С, Z или Ф либо код старших разрядов К4-К7. Для выработки следующего адреса микрокоманды по содержимому данных на шинах К4-К7 используется часть адреса текущей микрокоманды и несколько разрядов кода на шинах УА.

Управление схемой обработки признаков (C, Z и Ф) осуществляется с помощью микроинструкции на входах УФ0 – УФ3. Информация на входе Ф записывается в триггер Ф и затем в триггер С или Z. По входу ЗМ дается разрешение на запись информации со входов К в регистр адреса микрокоманд. Разрешение на прерывание выдается с выходной шины СРП при микроинструкции ПЕРЕХОД В НУЛЕВУЮ СТРОКУ, что означает конец выполнения микропрограммы (команды). Обычно сигнал с шины СРП подается на входную шину СРП блока приоритетного прерывания. Этот блок может ответить на прерывание выдачей сигнала подтверждения прерывания, что блокирует выдачу следующего выбранного адреса строки из БМУ. Тогда при выдаче нового адреса микрокоманды на линию адреса строки можно подавать адрес извне минуя БМУ, что позволяет перевести микропрограмму на программу обработки прерывания. Измененный адрес строки, переданный на адресные линии микрокоманд, не изменяет содержимого регистра адреса микрокоманд. Таким образом, последующая функция перехода будет использовать адрес строки в регистре адреса микрокоманды, а не измененный адрес строки.