Реферат: Специализированные модели управления (СМУ) систем технического зрения

Реферат: Специализированные модели управления (СМУ) систем технического зрения

Если ввести конвейерные регистры на выходах ОЗУИ и ПЗУ, то время цикла можно уменьшить в два раза.

Для tц = 200 нс; Т = 5,4 мс.

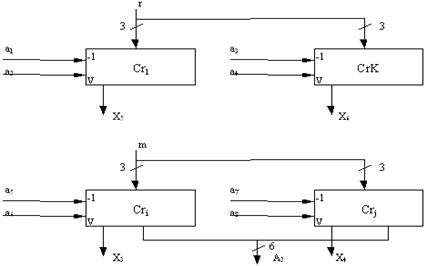

Рисунок 6 ¾ Организация блока счётчиков

4. Реализация СТЗ на базе однокристального микропроцессора (КР1810)

технический зрения микропроцессор аппаратный

Рассмотрим пример реализации СТЗ при использовании в качестве ВУ микропроцессора КР1810 ВМ8 При разработке будем использовать общий алгоритм рис.2.

Разработка структуры аппаратных средств

Для разработки структуры ВУ на базе МП КР1810 ВМ86 необходимо поставить в соответствие элементы и узлы рис.3 - 6 элементам и узлам МПК.

Один из вариантов такого соответствия приведён в табл.

Таблица 1 ¾ Варианты соответствия

| Переменные | Запоминающие узлы |

|

Хцн, Yцн |

16-разрядный регистр PXYЦ(входной порт) |

| M(n) | 8-разрядный регистр РМ(вх. порт) |

| r(p) | 8-разрядный регистр PR(вх. порт) |

| X,Y | 16-разрядный регистр РXY(выходной порт) |

|

Xт,Yт |

16-разрядной РОН ВР |

|

Rmin |

16-разрядные ячейки стека |

|

Xц, Yц |

16-разрядные ячейки стека |

| K | 8-разрядный РОН CH |

| L | 8-разрядный РОН CL |

| J | 8-разрядный РОН BH |

| I | 8-разрядный РОН BL |

|

A1(X’т,Y’т) |

16-разрядный РОН SI |

|

А2 |

16-разрядный РОН DI |

R |

16-разрядный РОН DX |

| Q | 16-разрядный РОН AX |

| EW | 1-разрядный регистр PEW (входной порт) |

Входные и выходные порты (регистры PXYЦ, РМ, PR, PXY, PEW) программно доступны МП как устройства ввода - вывода. Адреса регистров приведены в табл.2.

Таблица 2 ¾ Распределение адресов

Регистр |

Условное обозначение адреса |

Адрес |

| PXYЦ |

Port Xц |

00Н |

| PÌ | Port m | 02Н |

| PR | Port r | 03Н |

| PXY | Port X | 04Н |

| PEW | Port EW | 06Н |

Регистры могут быть выполнены на микросхемах КР580ИР82(83) или КР 580ИК55. Память изображения и эталонов является программно доступной со стороны процессора как память данных. Распределение главной памяти приведено в табл. 3.

Таблица 3 ¾ Распределение памяти

| ОЗУИ | 0000-3FFF |

| ПЗУ | 4000-40FF |

| СТЕК | 5000-50FF |

| Память программ | 6000-FFFF |

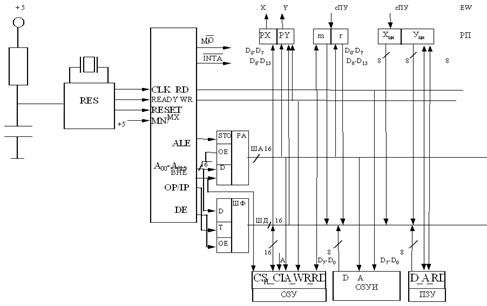

Координаты X и Y хранятся не в отдельных регистрах, а в одном 16 - ти разрядном регистре (ячейке памяти). Для адресации памяти достаточно 16 разрядов адреса. Регистры сегментов, кроме CS, перегружать после начальной установки не нужно. Адреса, выдаваемые по мультиплексированной шине адреса данных, запоминаются буферными регистрами К580 ИР82. Нагрузочная способность шины данных повышается шинными формирователями К580 ВА8 В рассматриваемом примере достаточно организовать работу МП в минимальном режиме. Структура ВУ на МП показана на рисунке 7.

Рисунок 7 ¾ Структура вычислительного устройства на МП4.2

Разработка программы функционирования

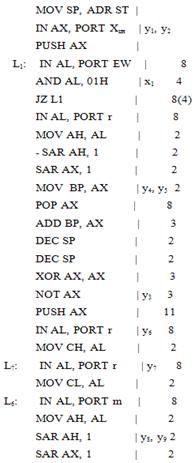

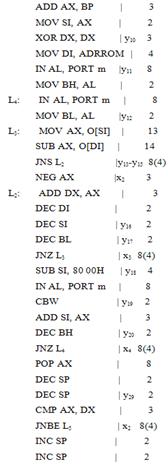

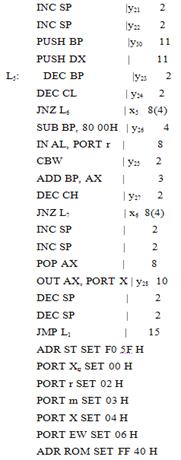

Программа разработана в соответствии с алгоритмом, показанным на рис. 2. На рис. 8 приведён текст программы на языке ассемблера и соответствие микрокоманд алгоритма.

Рисунок 8 ¾ Программа функционирования

Расчёт времени работы программы

Зная время выполнения каждой команды (см. рис. 8), можно определить общее время выполнения программы:

Т = [(((52m + 37)n + 97)r + 37)p+74]tц,

где tц определяется тактовой частотой процессора, tц = 200 нс.

Для m = n = 16 и r = p = 5; T = 70 мс.