Реферат: Синтез цифрового автомата управления памятью

Реферат: Синтез цифрового автомата управления памятью

| ba\dc | 00 | 01 | 11 |

|

ba\dc |

|

01 | 11 | 10 | |||

| 00 | 1 | 1 | 00 | 1 | 1 | |||||||

| 01 | 1 |

|

1 | 01 | 1 | 1 | ||||||

| 11 | 1 | 1 | 11 |

|

X | |||||||

| 10 | 1 | 1 | 1 | 10 | 1 | X |

Uвых1=cde v ade v abce v abcde v abce v bde v abce

| ba\dc |

|

01 | 11 | 10 | ba\dc |

|

01 |

|

10 | |||

|

|

1 | 00 | 1 | 1 | 1 | |||||||

|

|

1 | 1 |

|

01 | 1 |

|

1 | 1 | ||||

| 11 | 1 | 1 | 1 | 1 | 11 | 1 | X | |||||

| 10 | 1 | 1 | 10 |

|

X | 1 |

Uвых2=cde v ade v abe v bcde v bcde v bce v bde v abde

| ba\dc | 00 |

|

11 | 10 | ba\dc | 00 | 01 | 11 | 10 | |||

| 00 | 1 |

|

00 |

|

||||||||

| 01 |

|

1 |

|

1 | 01 |

|

|

1 | ||||

| 11 | 1 | 1 | 11 | 1 | 1 | X | 1 | |||||

| 10 |

|

1 | 1 | 10 | 1 | X | 1 |

Uвых3=bcd v abde v bcde v abde v bcde v ace v bde

| ba\dc |

|

|

11 | 10 | ba\dc | 00 |

|

|

10 | |||

| 00 | 1 | 1 | 1 | 1 | 00 | 1 | 1 | 1 | ||||

| 01 | 1 | 1 | 1 |

|

01 |

|

1 | 1 | 1 | |||

| 11 |

|

1 | 1 | 11 | 1 | X | ||||||

| 10 | 1 |

|

1 | 10 |

|

1 |

Uвых4=bde v abde v bс v dce v abce v abde v abcde v abcde v bde v abde

| ba\dc | 00 | 01 | 11 | 10 | ba\dc |

|

01 |

|

10 | |||

| 00 |

|

00 |

|

1 | ||||||||

| 01 | 1 | 01 | 1 |

|

1 | |||||||

| 11 | 1 |

|

1 |

|

X | 1 | ||||||

| 10 | 1 | 1 | 1 | 10 | 1 | 1 | X | 1 |

Uвых5=abce v abce v abde v acde v acde v bcde v abde v abe v cde v bde

Представим функции в базисе И-НЕ:

Uвых1=cde v ade v abce v abcde v abce v bde v abce

Uвых2=cde v ade v abe v bcde v bcde v bce v bde v abde

Uвых3=bcd v abde v bcde v abde v bcde v ace v bde

Uвых4=bde v abde v bс v dce v abce v abde v abcde v abcde v bde v abde

Uвых5=abce v abce v abde v acde v bcde v abde v abe v cde v bde

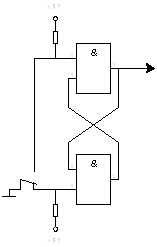

5. Схема сброса

Для устойчивой работы при необходимости, необходимо произвести сброс схемы в исходной в одно из заданных состояний (например в 0). Сброс будем производить при помощи кнопки сброса и логических элементов.

Схема сброса представлена на рисунке 6

рис. 6

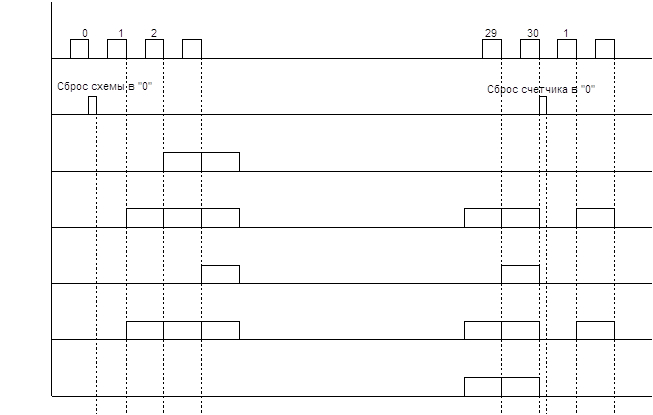

Принципиальная схема всего синтезируемого генератора цифровых сигналов представлена на рисунке 7.

Временная диаграмма работы данной схемы приведена на рисунке 8

рис. 8

ЗАКЛЮЧЕНИЕ

В соответствии с техническим заданием, в данном курсовом проекте было разработано устройство, формирующее последовательность цифровых сигналов для управления постоянным запоминающим устройством. Выполнение данной работы включало в себя все основные этапы проектирования цифровых устройств на интегральных микросхемах. Это позволило получить и закрепить практические навыки разработки структурной схемы устройства, синтеза и разработки его принципиальной схемы, конструктивной проработки изделия.

В заключении хотелось бы отметить, что разработанное устройство, а особенно формирователи выходных последовательностей оказались достаточно сложными и содержат большое количество корпусов интегральных микросхем.

00

00 00

00 11

11 00

00

01

01

1

1 1

1

00

00

01

01 11

11

1

1