Реферат: Проектирование Цифрового устройства

Реферат: Проектирование Цифрового устройства

Реферат: Проектирование Цифрового устройства

МИНИСТЕРСТВО ВЫСШЕГО ОБРАЗОВАНИЯ УКРАИНЫ

Сумской Государственный Университет

Кафедра Автоматики и Промышленной Электроники

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

к курсовому проекту по курсу: «Цифровая схемотехника»

по теме: «Проектирование Цифрового устройства»

ФЗ 51.6.090803.574ПЗ

Руководитель проекта Мировицкий Г. П.

Проектировал студент Симоненко А.В.

группы ПЭЗ-51

Оценка работы

Члены комиссии:

Сумы 1999

СОДЕРЖАНИЕ

ВВЕДЕНИЕ.............................................................................................................. 3

1. РАЗРАБОТКА СТРУКТУРНОЙ и ФУНКЦИОНАЛЬНОЙ СХЕМЫ УСТРОЙСТВА......................................................................................................... 5

1.1 Разработка структурной схемы устройства.......................................... 5

1.2 Разработка функциональной схемы устройства..................................... 6

2. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ УСТРОЙСТВА................... 8

2.1 Проектирование схемы детектора фронтов........................................... 8

2.2. Генератор тактовых импульсов............................................................... 9

2.3 Схема подсчета тактовых импульсов..................................................... 10

2.4 Схема преобразования параллельного кода в последовательный........... 11

2.5 Схема управления...................................................................................... 12

3. Заключение................................................................................................. 15

Список ЛИТЕРАТУРЫ..................................................................................... 16

ПРИЛОЖЕНИЕ 1. Алгоритм работы устройства.............................. 17

ВВЕДЕНИЕ

Внедрение микропроцессорной, и вообще цифровой, техники в устройства управления промышленными объектами требует от специалистов самого различного профиля быстрого освоения этой области знания. В процессе разработки функциональных схем цифровых устройств отчетливо выделяются два характерных этапа. На первом этапе, который можно назвать структурным проектированием, заданный неформально алгоритм разработчик представляет в виде последовательности некоторых операторов, таких, как получение результата, счет, преобразование кода, передача информации. При этом он старается использовать ограниченный набор общепринятых операторов. При использовании этих операторов, как правило, алгоритм можно представить довольно небольшим их числом. Структура алгоритма становится обозримой, понятной, легко читаемой и однозначной. На основе полученной структуры алгоритма формулируются технические требования к схемам, реализующим отдельные операторы. По техническим требованиям в качестве функциональных узлов схемы можно применить либо готовые блоки в интегральном исполнении, либо, если таких микросхем в наличии нет, синтезировать их из более простых элементов. Подобный синтез первоначально производится при помощи алгебры логики, после чего по полученным функциям строится эквивалентная схема. Однако, как правило, синтезированные схемы хуже их аналогов в интегральном исполнении. К этому приводят следующие обстоятельства: большее время задержки, большие габариты, большее потребление энергии. Поэтому результативного проектирования цифровых устройств разработчик должен уметь: выбрать наиболее приемлемый вариант решения поставленной задачи, работать с алгеброй логики, знать основные цифровые элементы и уметь их применять, по возможности знать наиболее простые и распространенные алгоритмы решения основных задач. Знание наиболее распространенных инженерных приемов в проектировании устройств позволит в будущем сразу воспользоваться готовой схемой, не занимаясь бесполезной работой. Необходимо заметить, что реализация схемы гораздо сложнее, чем простое решение задачи в алгебре логики и наборе полученной функции из логических элементов. В действительности даже, казалось бы, самые простые элементы, необходимо включать по определенной схеме, знать назначения всех выводов. Необходимо знать, чем различаются элементы в пределах серии. Понимание внутренней логики микросхемы особенно важно именно для специалистов по автоматике и промышленной электронике, поскольку цифровые микросхемы изначально создавались для выполнения строго определенных функций в составе ЭВМ. В условиях автоматики и радиотехники они часто выполняют функции, не запланированные в свое время их разработчиками, и грамотное использование микросхем в этих случаях прямо зависит от понимания логики их работы. Хорошее знание тонкостей функционирования схем узлов становится жизненно необходимым при поиске неисправностей, когда нужно определить, имеется ли неисправность в данном узле или же на его вход поступают комбинации сигналов, на которые схема узла не рассчитана. Составление тестов, а тем более разработка само проверяемых схем также требуют очень хороших знаний принципов работы узлов.

1. РАЗРАБОТКА СТРУКТУРНОЙ и ФУНКЦИОНАЛЬНОЙ СХЕМЫ УСТРОЙСТВА

1.1 Разработка структурной схемы устройства

Работу устройства можно представить следующим образом. По переднему фронту импульса начинается отсчет. При поступлении заднего фронта импульса или при превышении заданного интервала времени отсчет останавливается. Если значение в счетчике превышает заданный предел, на панели отображения выводится сигнал «ошибка». В противном случае на панели отображения отображается содержимое счетчика и величина измеренного интервала передается в устройство обработки. Описанный алгоритм отображен в приложении 1.

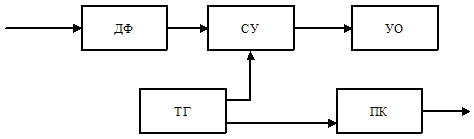

В состав структурной схемы войдут следующие элементы:

· Детектор фронтов

· Схема подсчета тактовых импульсов

· Тактовый генератор

· Схема преобразования параллельного кода в последовательный

· Схема отображения

Структурную схему можно представить так, как отображено на рисунке 2.

|

Рисунок 1. Структурная схема

При поступлении переднего фронта измеряемого импульса детектор фронтов (ДФ) формирует управляющий сигнал на начало счета. Формируемые тактовым генератором (ТГ) импульсы поступают на схему подсчета тактовых импульсов (СУ). При поступлении заднего фронта измеряемого импульса ДФ формирует сигнал останавливающий .счет. При этом количество подсчитанных импульсов выводится на схему отображения (УО) и через схему преобразования параллельного кода в последовательный (ПК) в устройство обработки.

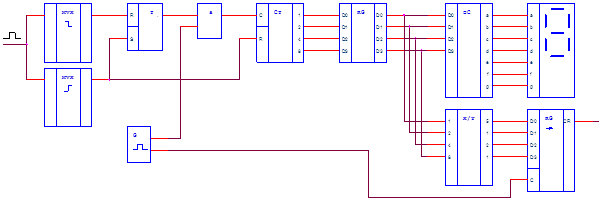

1.2 Разработка функциональной схемы устройства

Детектор фронтов состоит из двух ждущих мультивибраторов и триггера. Один ждущий мультивибратор предназначен для выделения заднего фронта импульса и сбрасывает триггер. Другой ждущий мультивибратор предназначен для выделения переднего фронта импульса и переключает триггер в единичное состояние и вырабатывает сигнал сброса счетчика. Оба мультивибратора вырабатывают импульсы длительности необходимой для надежного переключения триггера.

Схема подсчета тактовых импульсов состоит из элемента «И» и счетчика. Элемент «И» пропускает тактовые импульсы от генератора, только если триггер находится в единичном состоянии. Счетчик обеспечивает подсчет импульсов.

Схема отображения содержит регистр, дешифратор и индикаторы. Использование регистра позволяет избежать мерцания во время подсчета. Запись в регистр выполняется только по окончанию подсчета длительности импульса. Дешифратор необходим для преобразования двоично-десятичного кода в код обеспечивающий отображение соответствующей цифры.

|

Рисунок 2. Функциональная схема

Схема преобразования параллельного кода в последовательный состоит из преобразования кода 8421 в код 8421+3 и сдвигового регистра обеспечивающего преобразование параллельного кода в последовательный.

В состав тактового генератора входит генератор прямоугольных импульсов заданной частоты и делитель частоты для сдвигового регистра.

Определим разрядность индикатора по формуле:

![]() ,

,

где ![]() -

максимальное значение измеряемой величины;

-

максимальное значение измеряемой величины; ![]() -точность

измерения.

-точность

измерения.

![]()

Разрядность регистра с параллельным вводом и последовательным выводом информации определим исходя из того, что для отображения каждого десятичного разряда требуется 4 бита:

![]()

2. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ УСТРОЙСТВА

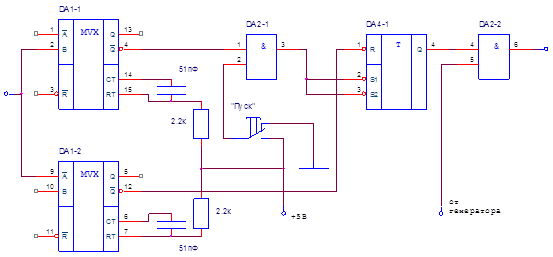

2.1 Проектирование схемы детектора фронтов

Рисунок 6. Схема детектора фронтов

|

Страницы: 1, 2