Реферат: Подсистема памяти современных компьютеров

Реферат: Подсистема памяти современных компьютеров

Память с синхронным интерфейсом — SDRAM и DDR SDRAM

Для вычислительного конвейера, в котором могут параллельно выполняться несколько процессов и запросов к данным, гораздо удобнее синхронный интерфейс. В этом случае все события привязываются к фронтам общего сигнала синхронизации, и система четко “знает”, что, выставив запрос на данные в таком-то такте, она получит их через определенное число тактов. А между этими событиями на шину памяти можно выставить и другой запрос, и если он адресован к свободному банку памяти, начнется скрытая (latency) фаза его обработки. Таким образом удается повысить производительность подсистемы памяти и ее шины, причем не за счет безумного увеличения числа проводов (увеличения разрядности и числа независимых банков, о чем будет сказано позже).

Микросхемы синхронной динамической памяти SDRAM (Synchronous DRAM) представляет собой конвейеризированные устройства, которые на основе вполне обычных ячеек (время доступа — 50–70 нс) обеспечивают цикл 5-1-1-1, но уже при частоте шины 100 МГц и выше. По составу сигналов интерфейс SDRAM близок к обычной динамической памяти: кроме входов синхронизации, здесь есть мультиплексированная шина адреса, линии RAS#, CAS#, WE (разрешение записи) и CS (выбор микросхемы) и, конечно же, линии данных. Все сигналы стробируются по положительному перепаду синхроимпульсов, комбинация управляющих сигналов в каждом такте кодирует определенную команду. С помощью этих команд организуется та же последовательность внутренних сигналов RAS# и CAS#, которая рассматривалась и для памяти FPM.

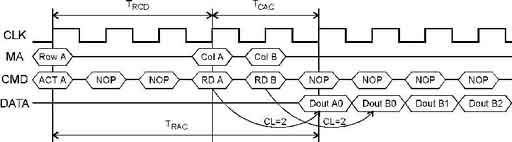

Каждая микросхема внутренне может быть организована как набор из 4 банков с собственными независимыми линиями RAS#. Для начала любого цикла обращения к памяти требуется подать команду ACT, которая запускает внутренний формирователь RAS# для требуемой строки выбранного банка. Спустя некоторое количество тактов можно вводить команду чтения RD или записи WR, в которой передается номер столбца первого цикла пакета. По этой команде запускается внутренний формирователь CAS#. Передача данных для циклов записи и чтения различается. Данные для первой передачи пакета записи устанавливаются вместе с командой WR. В следующих тактах подаются данные для остальных передач пакета. Первые данные пакета чтения появляются на шине через определенное количество тактов после команды. Это число, называемое CAS# Latency (CL), определяется временем доступа TCAC и тактовой частотой. В последующих тактах будут выданы остальные данные пакета. После обращения необходимо деактивировать банк — перевести внутренний сигнал RAS# в пассивное состояние, то есть произвести предзаряд (precharge). Это может быть сделано либо явно командой PRE, либо автоматически (как модифицированный вариант команд RD или WR. Внутренние сигналы CAS# формируются автоматически по командам обращения и дополнительных забот не требуют.

Регенерация выполняется по команде REF, за заданный период регенерации (стандартный 64 мс) должно быть выполнено 4096 или 8192 (в зависимости от объема микросхемы) команд REF.

На первый взгляд из этого описания не видно никаких особых преимуществ SDRAM по сравнению с BEDO. Однако синхронный интерфейс в сочетании с внутренней мультибанковой организацией обеспечивает возможность повышения производительности памяти при множественных обращениях. Здесь имеется в виду способность современных процессоров формировать следующие запросы к памяти, не дожидаясь результатов выполнения предыдущих. В SDRAM после выбора строки (активации банка) ее можно закрывать не сразу, а после выполнения серии обращений к ее элементам, причем как по записи, так и по чтению. Эти обращения будут выполняться быстрее, поскольку для них не требуется подачи команды активации и выжидания TRCD. Максимальное время удержания строки открытой ограничивается периодом регенерации. Возможность работы с открытой строкой была использована уже в FPM DRAM. Однако в SDRAM можно активировать строки в нескольких банках — каждую своей командой ACT, эта особенность и стоит за словами “Single-pulsed RAS# interface” в перечислении ключевых особенностей SDRAM. Активировать строку можно во время выполнения любой операции с другим банком. Обращение к открытой строке требуемого банка выполняется по командам RD и WR, у которых в качестве параметров кроме адреса столбца фигурирует и номер банка. Таким образом можно так спланировать транзакции, что шина данных в каждом такте будет нести очередную порцию данных, и такой поток будет продолжаться не только в пределах одного пакета, но и для серии обращений к разным областям памяти. Кстати, держать открытыми можно и строки в банках разных микросхем, объединенных общей шиной памяти.

Временная диаграмма чтения SDRAM

Микросхемы SDRAM оптимизированы для пакетной передачи. У них при инициализации программируется длина пакета и операционный режим. Пакетный режим может включаться как для всех операций (normal), так и только для чтения (Multiple Burst with Single Write). Этот выбор позволяет оптимизировать память для работы либо с WB, либо с WT-кэшем. Обратим внимание, что внутренний счетчик адреса работает по модулю, равному запрограммированной длине пакетного цикла (например, при длине пакета 4 он не позволяет перейти границу обычного четырехэлементного пакетного цикла).

Пакетные циклы могут прерываться (принудительно завершаться) последующими командами, при этом оставшиеся адреса отбрасываются. На рисунке приведен пример прерывания команды чтения по адресу A командой чтения по адресу B (подразумевается, что для адреса B строка уже открыта). В случае прерываний пакетов, как и при полных пакетах, шина данных при активированных банках может быть полезно нагруженной в каждом такте, за исключением случая чтения, следующего за записью. При этом шина будет простаивать CL тактов. В команде WR имеется возможность блокирования записи данных любого элемента пакета — для этого достаточно в его такте установить высокий уровень сигнала маскирования.

Микросхемы SDRAM имеют средства энергосбережения. В режиме саморегенерации Self Refresh микросхемы периодически выполняют циклы регенерации по внутреннему таймеру, в этом режиме они не реагируют на внешние сигналы и внешняя синхронизация может быть остановлена. В режиме пониженного потребления Power Down микросхема не воспринимает команды и регенерация не выполняется, поэтому длительность пребывания в нем ограничена периодом регенерации.

Синхронный интерфейс позволяет довольно эффективно использовать шину и обеспечить на частоте 100 МГц пиковую производительность 100 Мбит/пин (на 1 вывод шины данных). SDRAM используют в составе модулей DIMM с 8-байтной разрядностью, что дает производительность 800 Мбайт/с. Однако эта теоретическая производительность не учитывает накладные расходы на регенерацию и подразумевает, что требуемые страницы уже открыты. Из-за указанных выше ограничений на реальном произвольном потоке запросов производительность, конечно же, будет ниже. Потенциальные возможности почти одновременного обслуживания множества запросов, предоставляемая микросхемами SDRAM, будут реализованы лишь при достаточно “умном” контроллере памяти. От его предусмотрительности эффективность памяти зависит, пожалуй, больше, чем у простых FPM и EDO DRAM.

Память DDR SDRAM (Dual Data Rate — удвоенная скорость данных) представляет собой дальнейшее развитие SDRAM. Как и следует из названия, у микросхем DDR SDRAM данные внутри пакета передаются с удвоенной скоростью — они переключаются по обоим фронтам синхроимпульсов. На частоте 100 МГц DDR SDRAM имеет пиковую производительность 200 Мбит/пин, что в составе 8-байтных модулей DIMM дает производительность 1600 Мбайт/с. На высоких тактовых частотах (100 МГц) двойная синхронизация предъявляет очень высокие требования к точности выдерживания временных диаграмм. Для повышения точности синхронизации предпринят ряд мер.

Сигнал синхронизации микросхемы подается в дифференциальной форме, что позволяет снизить влияние смещения уровней на точность синхронизации.

Для синхронизации данных в интерфейс введен новый двунаправленный стробирующий сигнал DQS. Стробы генерируются источником данных: при операциях чтения DQS генерируется микросхемой памяти, при записи — контроллером памяти (чипсетом).

Для синхронизации DQS с системной тактовой частотой (CLK) микросхемы имеют встроенные схемы DLL (Delay Locked Loop) для автоподстройки задержки сигнала DQS относительно CLK. Эта схема работает наподобие фазовой автоподстройки (PLL) и способна выполнять синхронизацию (обеспечивать совпадение фронтов DQS и CLK) лишь в некотором ограниченном диапазоне частот синхронизации.

В отличие от обычных SDRAM, у которых данные для записи передаются одновременно с командой, в DDR SDRAM данные для записи (и маски DQM) подаются с задержкой на один такт (write latency). Значение CAS# Latency может быть и дробным (CL=2, 2.5, 3). Микросхемы SDRAM до “штатного” использования должны быть инициализированы — кроме предзаряда банков у них должны быть запрограммированы параметры конфигурирования. В DDR SDRAM из-за необходимости настройки цепей DLL программирование несколько сложнее.

Организация оперативной памяти

Теперь, имея общее представление о работе разных типов динамической памяти, обсудим варианты построения модулей памяти и “организационные” способы повышения производительности.

Микросхемы DRAM выпускают с разрядностью данных 1, 4, 8/9, 16/18 бит. Минимальной единицей упаковки, которая воспринимается системной платой компьютера, является банк памяти. Банк представляет собой объединение микросхем, обеспечивающее разрядность данных шины памяти. Так, для 386SX банк имеет разрядность 16 бит, для 386DX-486 — 32 бита, а для P5–P6 — 64 бита (8 байт). В банке все одноименные адресные входы микросхем и линии RAS# соединяются параллельно. Каждый банк выбирается своим сигналом RAS#. Линии CAS# или (и) WE должны быть индивидуальными для каждого байта, чтобы обеспечить возможность индивидуальной записи в любой байт банка. Микросхемы собираются в модули разрядностью 1 (SIMM-30, SIPP), 4 (SIMM-72) или 8 байт (DIMM). Модули могут содержать один или два банка микросхем (двусторонние модули). Однако полный банк памяти для машин с процессорами P5–P6 набирается парой модулей SIMM-72 или одним DIMM. Количество банков на системной плате ограничивается возможностями чипсета (количеством линий RAS#) или (и) количеством слотов для памяти. Первое ограничение является причиной известной проблемы с “двусторонними” модулями — в ряде плат установка такого модуля в один слот не позволяет использовать еще один слот. Увеличению числа слотов препятствует ограниченная нагрузочная способность шины памяти — каждый слот (тем более, с модулем) вносит паразитную емкость и индуктивность, ограничивающие быстродействие шины. Из-за влияния этой нагрузки для работы модулей SDRAM на частоте шины 100 МГц была разработана спецификация PC100, в которой кроме требований к быстродействию микросхем памяти задаются и правила разводки сигнальных и питающих проводников и прочие конструктивные нюансы. Теперь появляется и аналогичная спецификация PC133 — для частоты шины 133 МГц. Однако повышение тактовой частоты традиционной шины памяти технически сложно из-за большого числа сигнальных проводников. Популярные ныне модули DIMM SDRAM используют 32 адресных и управляющих линии и 64 (72 или 80 с контрольными) линии данных, при этом каждый дополнительный слот памяти требует еще несколько управляющих линий. На высоких частотах приходится учитывать задержки распространения сигналов в проводниках, и что самое неприятное — неодинаковость этих задержек, или перекос (skew).

Страницы: 1, 2, 3, 4, 5, 6, 7, 8