Реферат: Микропроцессорная система КР580

Реферат: Микропроцессорная система КР580

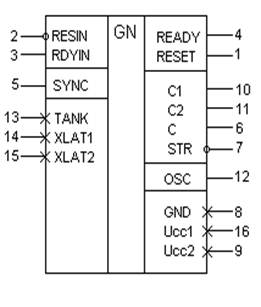

Отрицательный сигнал STSTB, длительность которого равна од--ному периоду частоты опорного генератора, формируется микросхемой КР580ГФ24 при поступлении на ее вход с микропроцессора КР580ВМ80А сигнала SYNC “Синхронизация”, свидетельствующего о начале машинного цикла.

При поступлении входного сигнала RESIN микросхема КР580ГФ24 с помощью триггера Шмитта и триггера Т1 вырабатывает сигнал RESET, синхронизированный с тактовым сигналом Ф2, По сигналу RESET осуществляется установка в исходное состояние различных устройств микропроцессорной системы. Наличие в микросхеме триггера Шмитта позволяет подавать на вход RESIN сигнал с пологим фронтом. С помощью триггера Т2 осуществляется стробиро-вание входного сигнала RDYIN “Готовность” тактовым сигналом Ф2.

Рисунок 5-Интегральное исполнение ИМС КР580ГФ24.

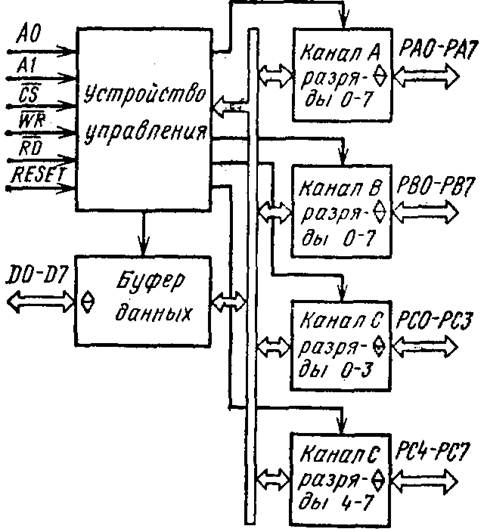

1.1.3 Интерфейс ввода- вывода ИМС КР580ВВ55А.

Микросхема КР580ВВ55А предназначена для параллельной передачи информации между

микропроцессором и периферийными устройствами и содержит три 8-разрядных канала ввода/вывода А, В, С.

Канал С может быть представлен в виде двух 4-разрядных каналов ввода/вывода, доступ к которым производится как к отдельным независимым каналам. Периферийные устройства подключаются к каналам А, В, С, а связь с микропроцессором осуществляется с помощью шины D через буфер данных. Каждый из каналов А, В, С состоит из 8-разрядного регистра и двунаправленных формирователей, имеющих на выходе состояние “Выключено”. Устройство управления содержит регистр управляющего слова (РУС), в который предварительно производится запись информации, определяющей режим работы каналов, и формирует сигналы выбора канала и управления каналом С.

Микросхема может работать в одном из трех режимов: режии О — простой ввод/вывод; режим 1 — стробируемый ввод/вывод; режим 2 — двунаправленный канал. Режим работы каналов можно изменять как в начале, так и в процессе выполнения программы, что позволяет обслуживать различные периферийные устройства в определенном порядке с помощью одной микросхемы КР580ВВ55А. Каналы А и В могут работать в различных

режимах, а работа канала С зависит от режимов работы каналов А и В, Комбинируя режимы работы каналов, можно обеспечить работу микросхемы почти с любым периферийным устройством.

Рисунок 6- Структурная схема КР580ВВ55А.

В режиме 0 осуществляется простой ввод/вывод данных по трем 8-разрядным каналам, причем канал С может использоваться как два 4-разрядных канала. Каждый из каналов может использоваться отдельно для ввода или вывода информации. В режиме О входная информация не запоминается, а выходная хранится в выходных регистрах до записи новой информации в канал или до записи нового режима.

В режиме 1 передача данных осуществляется только через каналы А и В, а линии канала С служат для приема и выдачи сигналов управления. Каждый из каналов А и В независимо

друг от друга может использоваться для ввода или вывода 8-разрядных данных, причем входные и выходные данные фиксируются в регистрах каналов.

В режиме 2 для канала А обеспечивается возможность обмена информацией о периферийными устройствами по 8-разрядному двунаправленному каналу. Для организации обмена используются пять линий канала С. В режиме 2 входные и выходные данные фиксируются во входном и выходном регистрах соответственно.

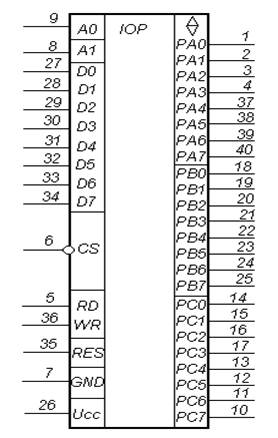

Таблица 3- Назначение выводов ИМС КР580ВВ55А.

|

Номер вывода |

Обозначение |

Назначение |

|

|

АО, А1 | Адрес |

| 27—34 | D7—DO | Шина данных |

![]()

![]()

Продолжение таблицы 3- Назначение

выводов ИМС КР580ВВ55А.

Продолжение таблицы 3- Назначение

выводов ИМС КР580ВВ55А.

| 37—40, 1—4 | РА7—РАО | Канал А |

| 5 | RD | Чтение |

| 6 | CS | Выбор микросхемы |

| 7 | GND | Общий |

| 10—13, 17, 16, 15, 14 | PC7—PCO | Канал С |

| 18—25 | PBO—PB7 | Канал В |

| 26 | Ucc | +5 В |

| 35 | RESET | Установка |

| 36 | WR | Запись |

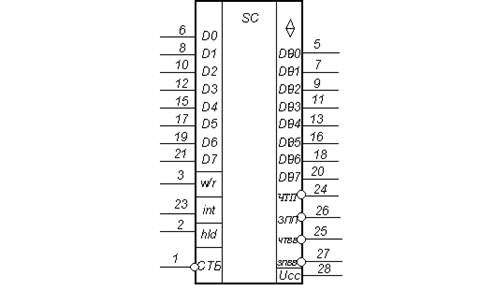

Рисунок 7- Интегральное исполнение интерфейса ввода- вывода.

1.1.4 Системный контроллер КР580ВК38.

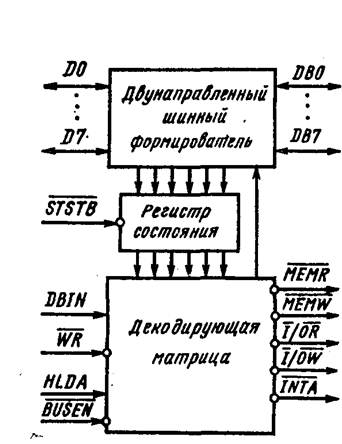

Микросхема КР580ВК38 выполняет функцию системного контроллера и шинного формирователя, осуществляет формирование управляющих сигналов обращения к ОЗУ или к устройствам ввода/вывода (УВВ) и обеспечивает прием и передачу 8-разрядной информации между шиной данных микропроцессора и системной шиной.

Формирование сигналов I/OW, MEMW в данной микросхеме происходит относительно сигнала STSTB “Строб состояния”, что позволяет при применении в микропроцессорной системе микросхемы КР580ВК38 использовать ЗУ и УВВ с более широким диапазоном быстродействия. . Двунаправленный шинный формирователь осуществляет буферирование 8-разрядной шины данных и автоматический контроль направления передачи данных.

Подключение системного контроллера к шине данных микропроцессора осуществляется с помощью двунаправленных выводов DO—D7, к системной шине—с помощью двунаправленных выводов DBO—DB7. При необходимости с помощью сигнала BUSEN “Управление системной шиной” выводы DBO—DB7 системного контроллера могут быть переведены в состояние “Выключено”.

![]()

![]() Таблица 4- Назначение выводов ИМС

КР580ВК38.

Таблица 4- Назначение выводов ИМС

КР580ВК38.

|

|

Обозначение |

Назначение |

| 6, 8, 10, 12, 15, 17, 19, 21 | DO—D7 | Шина данных |

| 5, 7, 9, 11, 13, 16, 18, 20 | DBO—DB7 | Системная шина |

| 1 | STSTB | Строб состояния |

| 2 | HLDA | Подтверждение захвата |

| 3 | WR | Запись |

| 4 | DBIN | Прием |

| 14 | GND | Общий |

| 22 | BUSEN | Управление системной шиной |

| 23 | INTA | Подтверждение прерывания |

| 24 | MEMR | Чтение памяти |

| 25 | I/OR | Чтение УВВ |

| 26 | MEMW | Запись в память |

| 27 | I/OW | Запись в УВВ |

| 28 | Ucc | +5 В |

Регистр состояния выполнен на шести D-триггерах и предназначен для хранения информации о состоянии микропроцессора, поступающей по шине данных DO—D7. Запись в регистр состояния осуществляется по сигналу STSTB, поступающему в начале каждого машинного цикла.

Декодирующая матрица в зависимости от режима работы микропроцессора, зафиксированного в регистре состояния, и входных управляющих сигналов HLDA, WR, DBIN формирует сигнал INTA “Подтверждение прерывания” или сигналы чтения/записи при обращении к ОЗУ или УВВ.

Рисунок 8- Интегральное исполнение ИМС КР580ВК38.

Рисунок 9- Структурная схема ИМС КР580ВК38.

1.1.5 Буферный регистр.

Микросхема КР580ИР82 представляет собой 8-разрядный буферный регистр, предназначенный для ввода и вывода информации со стробированием. Она может ильзоваться как в микропроцессорных системах, построенных на микросхемах серии КР580, так и в других вычислительных системах и устройствах дискретной автоматики.

Микросхема КР580ИР83 не содержит инвертирующие выходы. Данная микросхема имеет восемь триггеров D-типа и восемь выходных буферов, имеющих на выходе состояние “Выключено”. Управление передачей информации осуществляется с помощью сигнала STB “Строб”.