Реферат: Микро ЭВМ на основе МПК - 1804

Реферат: Микро ЭВМ на основе МПК - 1804

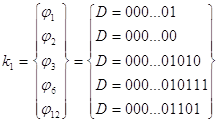

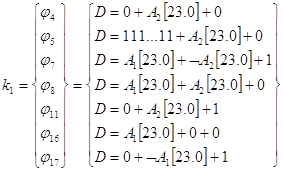

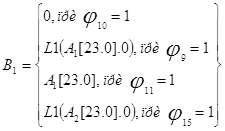

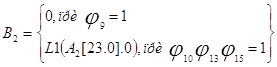

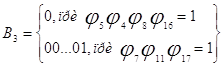

На основании полученных данных составим подмножества эквивалентных операторов:

;

;

;

;

![]()

![]()

![]()

![]()

![]()

Построим обобщенные операторы.

Класс ![]()

Для установки регистров

2. Класс ![]()

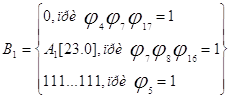

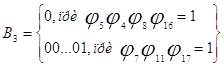

D = B1 + B2 + B3

При этом

Объединим классы k3, k4, k5, k7 в класс k8. Для этого обобщенный оператор примет вид:

Класс ![]() :

:

D = B1 + B2

Класс ![]() :

:

D = B1

![]()

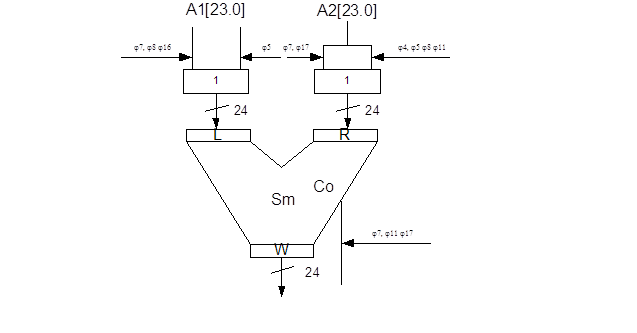

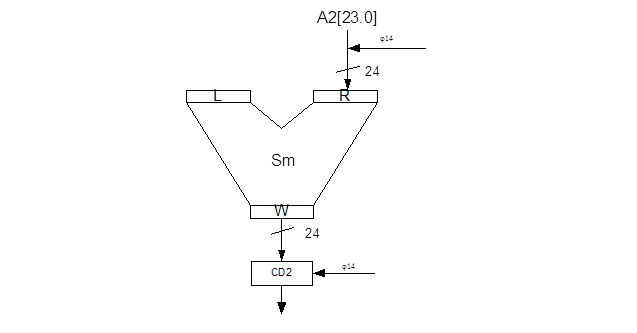

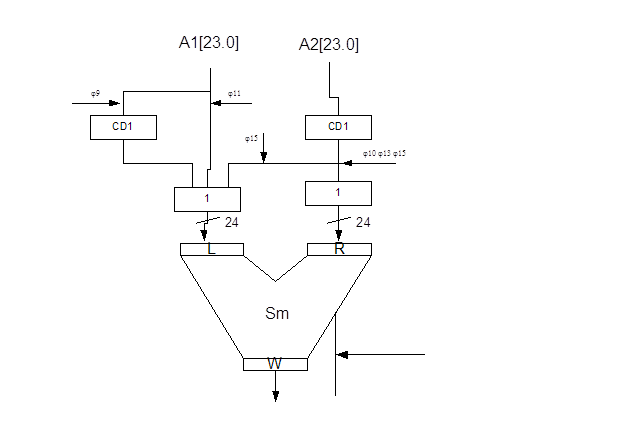

Построим структурные схемы узлов, реализующих обобщенные операторы:

Класс![]() :

:

Класс

Класс ![]() :

:

Класс![]() :

:

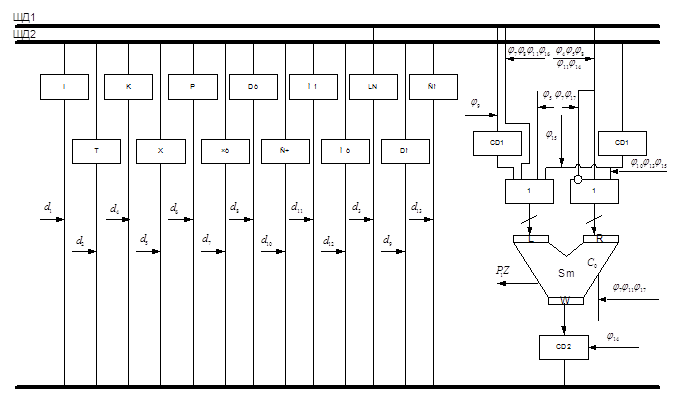

На основании полученных выше данных построим обобщенную схему операционного автомата. (Рис. 5).

Рис.

5. Обобщенная схема операционного автомата.

Рис.

5. Обобщенная схема операционного автомата.

1.4 Разработка управляющих автоматов для процессорных элементов микро ЭВМ.

При синтезе управляющего автомата условимся о следующих допущениях – комбинаторный сумматор, использованный при синтезе операционного автомата формирует следующие признаки:

P – знак числа

Число больше нуля – P = “0”

Число меньше нуля – P = “1”

Z – признак нуля

Число равно нулю – Z = “1”

Число не равно нулю – Z = “0”

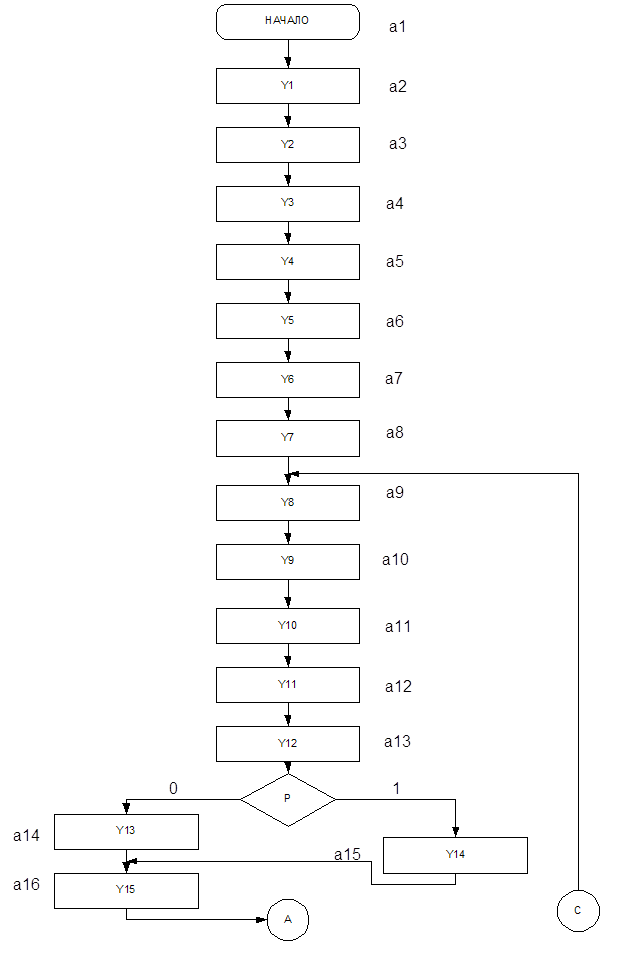

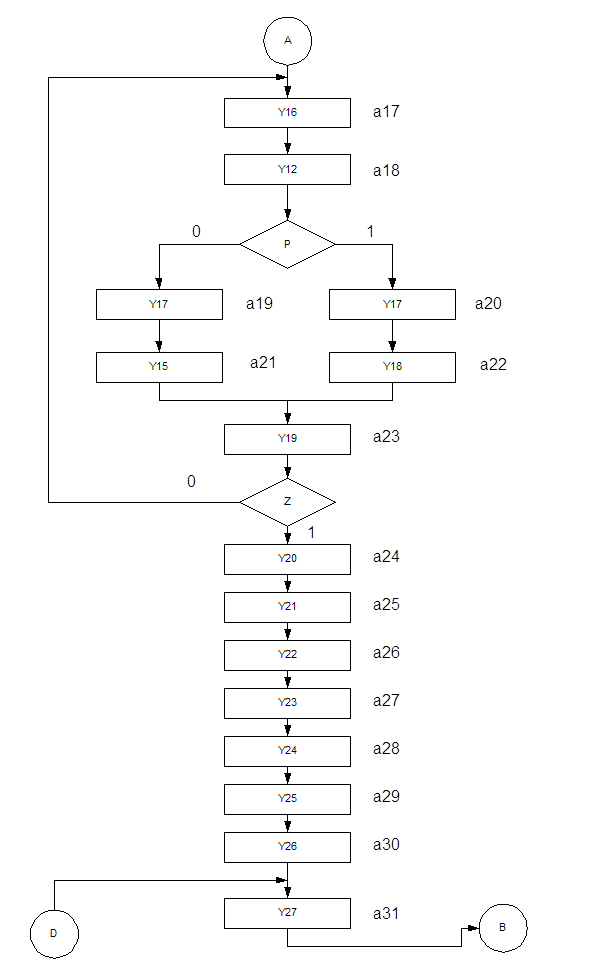

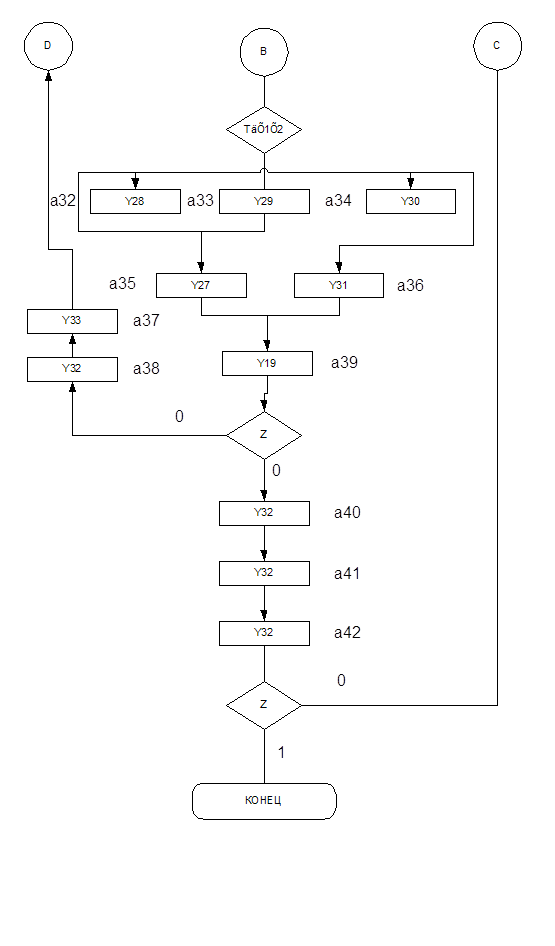

Для построения управляющего автомата произведем разметку ГСА (Рис. 6).

Рис. 6.1 Схема разметки ГСА.

Рис. 6.2 Схема разметки ГСА.

Рис. 6.3 Схема разметки ГСА.

|

|

|

|

|

|

|

|

|

|

000000 |

|

000001 | 1 | - | - |

|

|

000001 |

|

000010 | 1 |

|

D5 |

|

|

000010 |

|

000011 | 1 |

|

D5 D6 |

|

|

000011 |

|

000100 | 1 |

|

D4 |

|

|

000100 |

|

000101 | 1 |

|

D4 D6 |

|

|

000101 |

|

000110 | 1 |

|

D4 D5 |

|

|

000110 |

|

000111 | 1 |

|

D4 D5 D6 |

|

|

000111 |

|

001000 | 1 |

|

D3 |

|

|

001000 |

|

001001 | 1 |

|

D3 D6 |

|

|

001001 |

|

001010 | 1 |

|

D3 D5 |

|

|

001010 |

|

001011 | 1 |

|

D3 D5 D6 |

|

|

001011 |

|

001100 | 1 |

|

D3 D4 |

|

|

001100 |

|

001101 |

|

|

D3 D4 D6 |

|

|

001110 |

|

D3 D4 D5 | |||

|

|

001101 |

|

001111 | 1 |

|

D3 D4 D5 D6 |

|

|

001110 |

|

001111 | 1 |

|

D3 D4 D5 D6 |

|

|

001111 |

|

010000 | 1 |

|

D2 |

|

|

010000 |

|

010001 | 1 |

|

D2 D6 |

|

|

010001 |

|

010011 |

|

|

D2 D5 D6 |

|

|

010010 |

|

D2 D5 | |||

|

|

010010 |

|

010100 | 1 |

|

D2 D4 |

|

|

010011 |

|

010101 | 1 |

|

D2 D4 D6 |

|

|

010100 |

|

010110 | 1 |

|

D2 D4 D5 |

|

|

010101 |

|

010110 | 1 |

|

D2 D4 D5 D6 |

|

|

010110 |

|

010111 |

|

|

D2 |

|

|

010000 |

|

||||

|

|

010111 |

|

011000 | 1 |

|

D2 D3 |

|

|

011000 |

|

011001 | 1 |

|

D2 D3 D6 |

|

|

011001 |

|

011010 | 1 |

|

D2 D3 D5 D6 |

|

|

011010 |

|

011011 | 1 |

|

D2 D3 D4 |

|

|

011011 |

|

011100 | 1 |

|

D2 D3 D4 D6 |

|

|

011100 |

|

011101 | 1 |

|

D2 D3 D4 D5 |

|

|

011101 |

|

011110 | 1 |

|

D2 D3 D4 D5 D6 |

|

|

011110 |

|

011111 |

|

|

D1 |

|

|

100000 |

|

D1 D6 | |||

|

|

100001 |

|

D1 D5 D6 | |||

|

|

100011 |

|

D1 D5 | |||

|

|

100010 |

|

D1 D5 | |||

|

|

011111 |

|

100010 | 1 |

|

D1 D5 |

|

|

100000 |

|

100010 | 1 |

|

D1 D5 |

|

|

100001 |

|

100011 | 1 |

|

D1 D5 D6 |

|

|

100010 |

|

100110 | 1 |

|

D1 D4 D5 |

|

|

100011 |

|

100110 | 1 |

|

D1 D4 D5 |

|

|

100100 |

|

011110 | 1 |

|

D2 D3 D4 D5 |

|

|

100101 |

|

100100 | 1 |

|

D1 D4 |

|

|

100110 |

|

100101 |

|

|

D1 D4 D6 |

|

|

100111 |

|

D1 D4 D5 D6 | |||

|

|

100111 |

|

101000 | 1 |

|

D1 D3 |

|

|

101000 |

|

101001 | 1 |

|

D1 D3 D6 |

|

|

101001 |

|

000000 |

|

|

- |

|

|

001000 |

|

D3 |