Реферат: Курсовая по микропроцессорам

Реферат: Курсовая по микропроцессорам

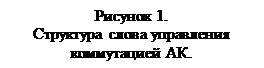

Режим коммутации определяется управляющим словом, записанным в регистр DD5, структура слова управления представлена на рис.1.

Слово управления АК записывается в регистр DD5 следующим образом:

на линии D5..D0 (РС5..РС0) МК выставляет логический “0”, и последний сигнал АС переводится в высокий уровень, таким образом данные с линий D5…D0 по положительному фронту сигнала АС записываются в регистр DD5.

2) Интерфейс RS-232.

Для организации интерфейса RS-232 использован встроенный в МК последовательный интерфейс связи. Вход приемника RS-232 (RxD) через преобразователь уровней (работу которого рассмотрим ниже) подключен к соответствующему входу МК RDI, а выход передатчика МК TDO через преобразователь уровней (ПУ) подключен к входам порта D MK (PD2…PD5 соответственно), а выходные сигналы RS-232 записываются МК в регистр хранения DD11, с выхода которого через ПУ подаются на соответствующие входы RS-232.

Запись выходных сигналов управления RS-232 (DTR, RTS) в регистр DD11 происходит следующим образом:

МК выставляет на линии D8, D9 требуемые уровни сигналов DTR, RTS , а на линии INT (PB5) низкий уровень, затем сигнал INT переводится в «1», по положительному фронту сигнала INT данные D8, D9 записываются в регистр DD11 и выдаются на его выходах и соответственно на выходах RS-232.

Как следует из анализа ТЗ в схеме организовано прерывание по изменению входных сигналов управления RS-232. Рассмотрим формирование сигнала прерывания IRQ на примере сигнала DCD:

Сигнал DCD после ПУ подается на вход элемента «исключающее или» DD3.1, на другой вход DD3.1 подается этот сигнал через диффиринцирующую цепь R11C1, т.е. при изменении сигнала DCD на втором входе сигнал изменится только через время t = 0,7R11C1, таким образом на это время на выходе DD3.1 будет сигнал высокого уровня, который через элементы ИЛИ DD4.1, DD4.3 и проинвертировавшись на DD2.2 подается на вход IRQ МК, тем самым вызвав прерывание выполнения основной программы и переход к подпрограмме обработки прерывания. Аналогично формируется сигнал прерывания от других входов RS-232, RI, DSR, CTS.

Выбор времени t = 0,7 · 100кОм · 470пФ = 33мкс произведен из следующих соображений:

МК должен принимать сигнал прерывания как по фронту так и по уровню; во время обработки внешнего прерывания МК не реагирует на другие запросы внешнего прерывания, вызванные изменением другого сигнала управления, а т.к. изменение уровня другого сигнала управления может произойти только после того, как МК изменит в результате обработки прерывания один из выходных сигналов RS-232, а это изменение должно быть в конце подпрограммы обработки прерывания, то длительность сигнала IRQ должна быть более продолжительная по времени выполнения команды RTI, т.е. более 21 машинного цикла или 10,5мкс, с двойным запасом получим 30мкс.

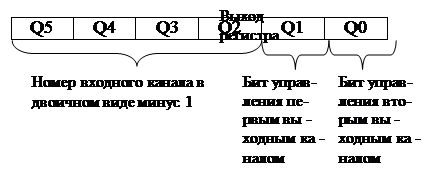

Перейдем к рассмотрению входных ПУ.

Как

известно, уровни сигналов RS-232 составляют: «0» от

–15В до –5В, «1» от +5В до+15В, а уровни КМОП 5В: «0» от –0,4В до +0,8В, «1» от

+3,5В до +5,4В. схема входного ПУ представлена на рисунке 2.

Как

известно, уровни сигналов RS-232 составляют: «0» от

–15В до –5В, «1» от +5В до+15В, а уровни КМОП 5В: «0» от –0,4В до +0,8В, «1» от

+3,5В до +5,4В. схема входного ПУ представлена на рисунке 2.

![]()

![]()

![]()

![]()

![]()

При подаче на

вход ПУ напряжения более +5В диод VD1 откроется и через

него и резистор R1 потечет ток, такой чтобы на выходе ПУ в

результате падения на резисторе R1 напряжение

составляло +5В+UVD . Где UVD – падение

напряжения на диоде VD1, которое зависит от тока через

него протекающего (чем меньше ток, тем меньше UVD,

для малых токов на нижней части ВАХ диода), но UVD

не может превышать 0,4В для относительно больших токов. Т.к. выходной

ток ИС КР1554 составляет доли мкА, чтобы уменьшить UVD

резистор R1 выбран относительно большим 1 МОм.

При подаче на

вход ПУ напряжения более +5В диод VD1 откроется и через

него и резистор R1 потечет ток, такой чтобы на выходе ПУ в

результате падения на резисторе R1 напряжение

составляло +5В+UVD . Где UVD – падение

напряжения на диоде VD1, которое зависит от тока через

него протекающего (чем меньше ток, тем меньше UVD,

для малых токов на нижней части ВАХ диода), но UVD

не может превышать 0,4В для относительно больших токов. Т.к. выходной

ток ИС КР1554 составляет доли мкА, чтобы уменьшить UVD

резистор R1 выбран относительно большим 1 МОм.

Аналогично ПУ работает при напряжении на входе меньше 0В ( ток течет через диод VD2).

Диоды VD1, VD2 являются встроенными защитными диодами ИС КР1554.

Резисторы R1…R5 необходимы для того, чтобы при отсутствии входных сигналов RS-232 входы ИС DD1.1 не оказались не подключенными, что не допустимо для КМОП ИС.

Выходные ПУ построены на ОУ DA1.1, DA1.2, DA2.1 включены по схеме компаратора с напряжением сравнения, формируемом на резистивных делителях R15R16, R18R19, R21R22, равным примерно 2,5В. резисторы R17, R20, R23 применены для защиты выходов ОУ от КЗ.

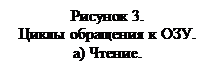

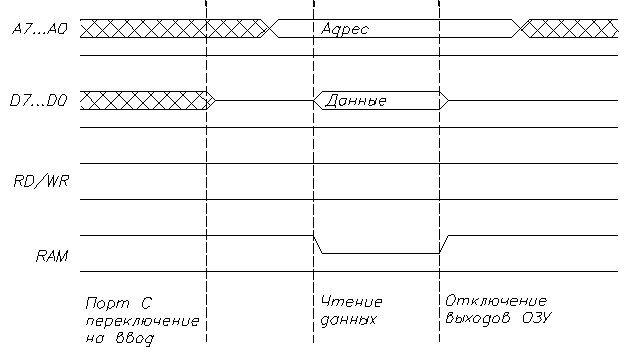

3) Оперативное запоминающее устройство.

|

Адресные входы ОЗУ DD10 подключены к шине адреса А7…А0 (порт А МК), входы/выходы данных DD10 подключены к шине данных D7…D0 (порт С). Всегда, кроме времени обращения МК к ОЗУ, сигналы RD/WR, подключенный к соответствующему входу DD10 (линия РВ2) и RAM, подключенный к входам «выбора ИС» (СЕ) и «разрешения выходов» (ОЕ) (линия РВ1) должны находиться в состоянии логической «1», т.е. выходы DD10 отключены от шины данных.

|

Циклы обращения к ОЗУ представлены на рисунке 3.

4) Цифроаналоговый преобразователь (ЦАП).

Блок ЦАП состоит непосредственно из самой ИС ЦАП DD12 с выходным ОУ DA3.2 и схемы формирования опорного напряжения. Схема формирования опорного напряжения состоит из параметрического стабилизатора R3VD1 с напряжением стабилизации 10В и масштабирующего усилителя на ОУ DA3.1 и R31…R33, с помощью подстроечного резистора R32 опорное напряжение должно регулироваться в пределах от –5В до минимального выходного напряжения ОУ –13В. Резистор R34 предназначен для защиты ОУ DA3.2 от КЗ.

Необходимо отметить, что т.к. на два младших разряда ЦАП всегда подан низкий уровень, то на выходе ЦАП максимальное напряжение не будет достигать опорного напряжения.

Запись цифрового кода во внутренний регистр DD12 происходит следующим образом:

МК выставляет на шину данных D7…D0 (PC7…PC0) младший байт кода, затем выставляются два старших разряда кода на D9, D8 (PB7, PB6) и одновременно сигнал D/A (PB3) переводится в высокий уровень, на выходе ЦАП появляется аналоговый сигнал соответствующий цифровому коду, чтобы «защелкнуть» код во входном регистре DD12 необходимо перевести сигнал D/A в низкий уровень, не изменяя сигналы на D8, D9.

Следует заметить, что во время обращения к ЦАП до «защелкивания» данных необходимо запрещать внешние прерывания, т.к. для регистра выходов RS-232 также используются линии D8, D9.

5) Выходные дискретные сигналы.

Выходные дискретные сигналы записываются в регистры DD13, DD14 следующим образом:

МК выставляет необходимые данные на линии D7…D0 (порт С), а затем на линии D8, D9 (PB6, PB7) и одновременно уровень логического «0» на линию OUT (PB4), после этого не изменяя данных, сигнал OUT переводится в логическую «1». Также как в случае с ЦАП необходимо запрещать внешние прерывания до перехода OUT в высокий уровень.

Выходы регистров DD13, DD14 являются выходными дискретными сигналами ТТЛ, т.к. выходные уровни КМОП 5В согласуются с входными уровнями ТТЛ, а выходной ток ИС серии КР1554 достаточно велик (до 20мА).

5. Литература.

1. Микросхемы для бытовой радиоаппаратуры. Справочник. Новаченко И.В. и др. – М.: Радио и связь, 1989г.

2. Интегральные микросхемы: Микросхемы для аналого-цифрового преобразования и средств мультимедиа. Выпуск 1. – М.: ДОДЭКА, 1996г.

3. Проектирование импульсных и цифровых устройств радиотехнических систем. Под ред. Казаринова Ю.М. – М.: Высшая школа, 1985г.

4. Потемкин И.С. функциональные узлы цифровой автоматики. – М.: Энергоатомиздат, 1988г.

5. Зельдин Е.А. цифровые интегральные микросхемы в информационно-измерительной аппаратуре. – Л.: Энергоатомиздат, 1986г.

6. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах. Справочник. – М.: Радио и связь, 1990г.

7. Уильямс Г.Б. Отладка микропроцессорных систем. – М.: Энергоатомиздат, 1988г.

8. Шило В.Л. Популярные цифровые микросхемы. Справочник. – М.: Радио и связь, 1988г.

9. Цифровые интегральные микросхемы. Справочник. Мальцев П.П. и др. – М.: Радио и связь, 1994г.

10. Логические интегральные схемы КР1553, КР1554. Справочник. – ТОО «БИНОМ», 1993г.

11. Аванесян Г.Р., Левшин В.П. Интегральные микросхемы ТТЛ, ТТЛШ. Справочник. - М.: Машиностроение, 1993г.

12. Разработка и оформление конструкторской документации радиоэлектронной аппаратуры. Справочник. Под ред. Романычевой Э.Т. – М.: Радио и связь, 1989г.