Реферат: Конспект лекций по микропроцессорной технике

Реферат: Конспект лекций по микропроцессорной технике

Реферат: Конспект лекций по микропроцессорной технике

КОНСПЕКТ ЛЕКЦИЙ

по дисциплине «Микропроцессорная техника»

Микропроцессорные и программные средства автоматизации.

Микропроцессорный комплект

Серии К1810

Состав: К1810ВМ86 – центральный процессор (16 бит)

ВМ88 – центральный процессор с восьмибитной шиной данных;

ВМ87 – арифметический сопроцессор;

ВМ59 – процессор ввода/вывода;

ГР84 – генератор тактовых импульсов;

ВГ88 – контроллер системной шины;

ВБ89 – арбитр системной шины

ВТ02 – контроллер для подключения динамической памяти объемом

16 Кбайт

ВТ03 - контроллер для подключения динамической памяти объемом

64 Кбайт

ВН54 – интервальный таймер

ВТ37 – контроллер прямого доступа к памяти

ВН59 – программируемый контроллер прерываний

ИР86/87 – шинные формирователи (с инверсией / без инверсии)

ИР82/83 - регистры-защелки (с инверсией / без инверсии)

Микросхема К1810ВМ86 (Intel 8086).

Шестнадцатиразрядный однокристальный МП выполняющий около 2 млн. операций в секунду. Синхронизируется тактовой частотой 25 МГЦ.

Имеет 20-ти разрядную шину адреса, что позволяет обеспечить прямую адресацию 1 Мбайт внешней памяти. Область адресного пространства памяти разбита на сегменты по 64 Кб. Такая организация памяти обеспечивает удобный механизм вычисления физических адресов . ША и ШД мультиплексированы. При организации вычислительных систем их нужно разделить (регистры-защелки). МП может обращаться как к памяти, так и к внешним устройствам.

При обращении к внешним устройствам используются 16 младших линий ША. Следовательно можно подключить 64 К 8-битных внешних устройств, либо 32 К 16-ти разрядных. МП имеет многоуровневую систему прерываний: 256 векторов прерываний. Данный МП является дальнейшим совершенствованием К580ВМ80. Система команд сходна, но более расширена. Программное обеспечение легко переводится с одного МП на другой.

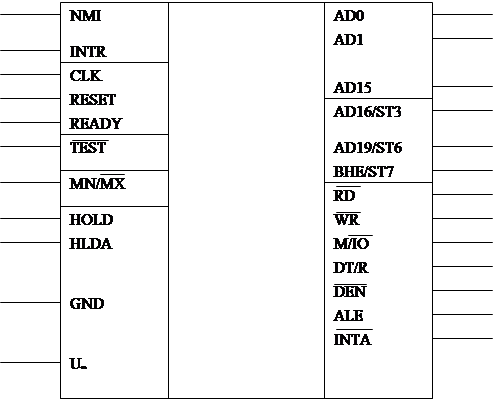

Функциональная схема:

См. рис.

В первый такт обмена на AD0-15 устанавливаются младшие 16 бит адреса памяти или адрес внешнего устройства, сопровождается эта информация сигналом ALE. Во втором такте обмена выставляются данные, которые сопровожда-

ются сигналом DEN. ALE и DEN управляют регистрами-защелками. AD16/ST3-AD19/ST6 – мультиплексированные линии адреса состояния.

В первый такт обмена выдается 4 старших разряда адреса памяти, а при обращении к внешнему устройству – нули. Во втором такте выдаются сигналы состояния МП, причем сигналы ST3-ST4 определяют сегментный регистр участвующий в формировании физического адреса.

| ST3 | ST4 | Рег. |

|

0 1 0 1 |

0 0 1 1 |

SS CS DS |

Сегментные регистры. Участвуют в формиро- вании физического адреса.

![]() ST5

– дублирует состояние флага разрешения прерываний.

ST5

– дублирует состояние флага разрешения прерываний.

BHE – разрешение старшего байта. Работает совместно с сигналом А0, обеспечивая механизм передачи информации по ШД.

|

|

A0 | Вид передачи данных |

|

0 0 1 1 |

0 1 0 1 |

Передается 16-ти битное слово Передается старший байт AD8-AD15 Передается младший байт AD0-AD7 Нет обращения |

![]()

|

|

|

|

![]() WR –

сигнал записи.

WR –

сигнал записи.

![]() M/IO – обращение к памяти или внешним

устройствам.

M/IO – обращение к памяти или внешним

устройствам.

![]() DT/R – направление передачи

информации:

DT/R – направление передачи

информации:

«1» - в МП; «0» - из МП.

INTA, INTR – запрос на маскируемое прерывание (INTA – подтверждение прерывания).

NMI – запрос на немаскируемое прерывание.

HOLD – запрос на переход в режим прямого доступа к памяти.

HLDA – подтверждение захвата шины.

![]() TEST

– проверочный вход, используется в команде WAIT для

организации холостых тактов: «1» - МП выполняет «0», с периодичностью 5 Т

проверяет состояние этого сигнала.

TEST

– проверочный вход, используется в команде WAIT для

организации холостых тактов: «1» - МП выполняет «0», с периодичностью 5 Т

проверяет состояние этого сигнала.

MN/MX – минимальный / максимальный режимы, определяющие конфигурацию вычислительной системы. MN- ограничение объема памяти и т.д.

Архитектура МП.

МП содержит в своем составе 14 регистров общего назначения.

AX=AH+AL

BX=BH+BL

CX=CH+CL

DX=DH+DL

Все остальные регистры общего назначения являются неделимыми:

![]()

![]() SP

используются при обращениях к стеку для хранения

SP

используются при обращениях к стеку для хранения

BP адресной информации

SI при обращении к памяти или внешнему устройству

DI

Сегментные регистры:

CS – определят начальный адрес сегмента кода в котором хранится программа;

SS – хранит начальный адрес сегмента стека;

DS – начальный адрес сегмента данных;

ES – начальный адрес дополнительного сегмента под данные;

IP – хранит смещение очередной команды переданной для выполнения.

DA=CS+IP

F- регистр флагов

| 0F | DF | IF | SF | ZF | AF | PF | CF |

AD15 AD0

CF – флаг переноса, фиксирует возникновение переноса при сложении или заеме при вычитании, а также выдвижение старшего байта при операциях сдвига;

PF- флаг четности, фиксирует четное число;

AF – флаг вспомогательного переноса, фиксирует перенос или заем из разряда D4 в D3 при операции сложения и из D3 в D4 при вычитании. Используется при преобразовании кодов из двоичного в двоично-десятичный и наоборот;

ZF – флаг нуля, сигнализирует о получении нулевого результата;

SF – флаг знака, дублирует состояние старшего бита результата операции;

OF – флаг переполнения разрядной сетки, сигнализирует о потере старшего бита при сложении.

Названные 6 флагов сигнализируют о результатах арифметических операций. Оставшиеся 3 флага относятся к флагам управления:

DF – флаг направления обработки команд программы, «0» -выполняется команда от меньших адресов к большим.

IF – флаг разрешения прерываний, если он установлен, то процессор реагирует на запросы прерывания по входу INTR;

TF – флаг трассировки, «1» - МП выполняет команды программы в пошаговом режиме.

В состав МП входит устройство управления, которое дешифрует команды и обеспечивает соответствующие управляющие сигналы. Имеется регистр – очередь команд объемом 6 байт в который загружается очередная команда предназначенная для выполнения. Буфер шины адреса – данных представляет собой 16 двунаправленных усилителей, обеспечивающих номинальную нагрузочную способность шины. Буфер адреса состоит из 4-х двунаправленных усилителей выполняющих аналогичную функцию. Сумматор адресов служит для вычисления физических адресов ячеек памяти. АЛУ – 16-ти разрядное.

Сегментация памяти и вычисление адресов.

Память в ЭВМ на базе К1810ВМ86 организуется как одномерный массив байтов, каждый из которых имеет свой 20-разрядный физический адрес(00000-FFFFF).

Порядок размещения данных в памяти обычный: слово занимает 2 соседние ячейки памяти, причем первым идет младший байт слова, а вторым старший. Физическим адресом слова считается адрес младшего байта слова.

20-ти битный физический адрес ячейки памяти содержится в объекте: сегмент + смещение. Причем на сегмент и на смещение отводится по 2 байта. Следовательно полный физический адрес размещается в 4-х ячейках памяти.