Курсовая работа: Пространственно-временной коммутатор 7x7

Курсовая работа: Пространственно-временной коммутатор 7x7

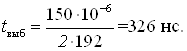

Тип микросхемы выбираем по критериям быстродействия и емкости. Быстродействие запоминающего устройства определяется временем выборки адреса:

![]()

где Тц =125 мкс - длительность цикла; ![]() – количество каналов,

которое должно быть коммутировано (в принципе, для работы данного коммутатора

достаточно

– количество каналов,

которое должно быть коммутировано (в принципе, для работы данного коммутатора

достаточно ![]() каналов,

однако, чтобы не нарушать типовую структуру коммутатора, с восьмой тракт будем

записывать только нули или единицы).

каналов,

однако, чтобы не нарушать типовую структуру коммутатора, с восьмой тракт будем

записывать только нули или единицы).

Емкость запоминающего устройства определяется числом входящих ИКМ трактов и разрядностью передаваемых сигналов. Как уже отмечалось, для реализации варианта пространственно-временного коммутатора 7х7 достаточна емкость 168 слов по 8 бит каждое, однако для расчета принимаем емкость запоминающих устройств в коммутаторе 8х8 (т. к. в данном проекте не производим преобразование частоты, и имеем в параллельном коде 8 битные каналы, из которых 1 бит не несет полезной информации) равную 192 слова по 8 бит.

РЗУ работает с управлением по записи, причем учитывается сквозная нумерация, приведенная в приложении А, номера входящих сдвигаем на 8 позиций (рассматриваем 18 входящий – подразумеваем 10).

РЗУ и АЗУ построены на основе микросхемы КМ185РУ7. Параметры микросхемы, назначение выводов и таблица истинности микросхемы КМ185РУ7 приведены в таблицах 4.4–4.6.

Рис. 4.3. Микросхема КМ185РУ7.

Таблица 4.4

Параметры микросхемы КМ185РУ7

| Информационная емкость | 1024 бит |

| Организация | 256 слов´4 разряда |

| Напряжение питания |

5 В |

| Потребляемая мощность | не более 710 мВт |

| Диапазон температур | -10…+700С |

| Совместимость по входу и выходу | с ТТЛ - схемами |

|

Входное напряжение низкого уровня высокого уровня |

не более 0,8 В не менее 2,1 В |

|

Входное напряжение низкого уровня высокого уровня |

не более 0,45 В не менее 2,4 В |

|

Входной ток низкого уровня высокого уровня |

не более 0,3 мА не менее 0,04 мА |

|

Выходной ток низкого уровня высокого уровня |

не более 8 мА не менее 5,2 мА |

| Время выборки адреса tА(А) | не более 45 нс |

| Время выбора tСS | не более 30 нс |

| Время выборки считывания tА(RD) | не более 40 нс |

| Время выборки сигнала разрешения по выходу tА(СЕО) | не более 30 нс |

| Время установления сигнала записи относительно адреса tSU(А-WR) | не менее 10 нс |

| Время установления сигнала записи относительно входных данных tSU(DI-WR) | не менее 5 нс |

| Длительность сигнала записи tW(WR) | не менее 30 нс |

| Время сохранения адреса после сигнала записи tV(WR-A) | не менее 5 нс |

| Время сохранения входных данных после сигнала записи tV(WR-DI) | не менее 5 нс |

| Время восстановления высокого сопротивления или время восстановления высокого уровня при подключении RL к UCC после сигнала СS tDIS(CS) | не более 30 нс |

| Время восстановления высокого сопротивления или время восстановления высокого уровня при подключении RL к UCC после сигнала СЕО tDIS(CEO) | не более 30 нс |

| Время восстановления высокого сопротивления после сигнала считывания tDIS(RD) | не более 35 нс |

| Время цикла записи tCY(WR) | не менее 45 нс |

Таблица 4.5