Доклад: Сравнительные характеристики современных аппаратных платформ

Доклад: Сравнительные характеристики современных аппаратных платформ

UltraSPARC поддерживает различные алгоритмы компрессии, используемые для разнообразных видеоприложений и обработки неподвижных изображений, включая H.261, MPEG-1, MPEG-2 и JPEG. Более того, он может обеспечивать скорости кодирования и декодирования, необходимые для организации видеоконференций в реальном времени.

Первые системы на базе нового процессора

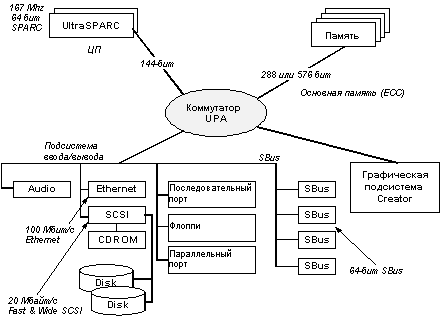

В настоящее время Sun выпускает два типа настольных рабочих станций и серверов, оснащенных процессорами UltraSPARC: Ultra 1 и Ultra 2 (рисунок 6.9). В моделях Ultra 1 используются процессоры с тактовой частотой 143 и 167 МГц. При этом они комплектуются как стандартными видеоадаптерами TurboGX и TurboGXplus (модели 140 и 170), так и новыми мощными видеоподсистемами Creator и Creator3D (модель 170Е), позволяют наращивать объем оперативной памяти до 512 Мбайт, внутренних дисков до 4.2 Гбайт и устанавливать накопители на магнитной ленте, флоппи-дисководы и считывающие устройства с компакт-дисков. Эти системы обеспечивают уровень производительности в 252 SPECint92 и 351 SPECfp92 при тактовой частоте 167 МГц. Модели 170Е оснащаются контроллерами Fast&Wide SCSI-2 и 100Base-T Ethernet.

Модели Ultra 2 - это однопроцессорные и двухпроцессорные системы на базе 200 МГц процессора UltraSPARC (332 SPECint92 и 505 SPECfp92), имеющие максимальный объем оперативной памяти 1 Гбайт. Появление следующих моделей, построенных на процессорах UltraSPARC II (420 SPECint92 и 660 SPECfp92), ожидается в середине 1996 года.

Таким образом, выпуск 64-битового процессора UltraSPARC и первых компьютеров на его основе ознаменовал собой новый этап в развитии Sun Microsystems. Компания планирует постепенно перевести на эти процессоры все свои изделия, включая рабочие станции и серверы начального уровня. Конечно для широкого внедрения новой концепции обработки данных, получившей название UltraComputing, понадобится некоторое время, но уже сейчас очевидно, что ориентация Sun на обеспечение высокой сбалансированной производительности для широкого класса прикладных систем, высокой пропускной способности передачи данных для сетевых приложений и построение эффективных средств визуализации и обработки видеоданных в реальном времени позволяет ей сохранять лидирующие позиции на современном рынке компьютеров для научно-технических и бизнес-приложений.

Рис. 6.9. Архитектура компьютеров Ultra 1 и Ultra 2

Процессоры PA-RISC компании Hewlett-Packard

Основой разработки современных изделий Hewlett-Packard является архитектура PA-RISC. Она была разработана компанией в 1986 году и с тех пор прошла несколько стадий своего развития благодаря успехам интегральной технологии от многокристального до однокристального исполнения. В сентябре 1992 года компания Hewlett-Packard объявила о создании своего суперскалярного процессора PA-7100, который с тех пор стал основой построения семейства рабочих станций HP 9000 Series 700 и семейства бизнес-серверов HP 9000 Series 800. В настоящее время имеются 33-, 50- и 99 МГц реализации кристалла PA-7100. Кроме того выпущены модифицированные, улучшенные по многим параметрам кристаллы PA-7100LC с тактовой частотой 64, 80 и 100 МГц, и PA-7150 с тактовой частотой 125 МГц, а также PA-7200 с тактовой частотой 90 и 100 МГц. Компания активно разрабатывает процессор следующего поколения HP 8000, которые будет работать с тактовой частотой 200 МГц и обеспечивать уровень 360 единиц SPECint92 и 550 единиц SPECfp92. Появление этого кристалла ожидается в 1996 году. Кроме того, Hewlett-Packard в сотрудничестве с Intel планируют создать новый процессор с очень длинным командным словом (VLIW-архитектура), который будет совместим как с семейством Intel x86, так и семейством PA-RISC. Выпуск этого процессора планируется на 1998 год.

PA 7100

Особенностью архитектуры PA-RISC является внекристальная реализация кэша, что позволяет реализовать различные объемы кэш-памяти и оптимизировать конструкцию в зависимости от условий применения (рисунок 6.10). Хранение команд и данных осуществляется в раздельных кэшах, причем процессор соединяется с ними с помощью высокоскоростных 64-битовых шин. Кэш-память реализуется на высокоскоростных кристаллах статической памяти (SRAM), синхронизация которых осуществляется непосредственно на тактовой частоте процессора. При тактовой частоте 100 МГц каждый кэш имеет полосу пропускания 800 Мбайт/с при выполнении операций считывания и 400 Мбайт/с при выполнении операций записи. Микропроцессор аппаратно поддерживает различный объем кэш-памяти: кэш команд может иметь объем от 4 Кбайт до 1 Мбайт, кэш данных - от 4 Кбайт до 2 Мбайт. Чтобы снизить коэффициент промахов применяется механизм хеширования адреса. В обоих кэшах для повышения надежности применяются дополнительные контрольные разряды, причем ошибки кэша команд корректируются аппаратными средствами.

Рис. 6.10. Блок-схема процессора PA 7100

Процессор подсоединяется к памяти и подсистеме ввода/вывода посредством синхронной шины. Процессор может работать с тремя разными отношениями внутренней и внешней тактовой частоты в зависимости от частоты внешней шины: 1:1, 3:2 и 2:1. Это позволяет использовать в системах разные по скорости микросхемы памяти.

Конструктивно на кристалле PA-7100 размещены целочисленный процессор, процессор для обработки чисел с плавающей точкой, устройство управления кэшем, унифицированный буфер TLB, устройство управления, а также ряд интерфейсных схем. Целочисленный процессор включает АЛУ, устройство сдвига, сумматор команд перехода, схемы проверки кодов условий, схемы обхода, универсальный регистровый файл, регистры управления и регистры адресного конвейера. Устройство управления кэш-памятью содержит регистры, обеспечивающие перезагрузку кэш-памяти при возникновении промахов и контроль когерентного состояния памяти. Это устройство содержит также адресные регистры сегментов, буфер преобразования адреса TLB и аппаратуру хеширования, управляющую перезагрузкой TLB. В состав процессора плавающей точки входят устройство умножения, арифметико-логическое устройство, устройство деления и извлечения квадратного корня, регистровый файл и схемы "закоротки" результата. Интерфейсные устройства включают все необходимые схемы для связи с кэш-памятью команд и данных, а также с шиной данных. Обобщенный буфер TLB содержит 120 строк ассоциативной памяти фиксированного размера и 16 строк переменного размера.

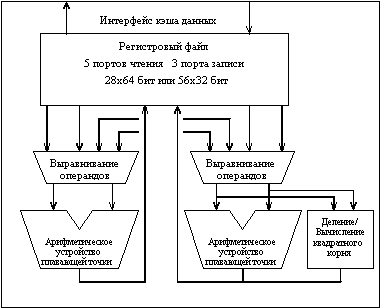

Устройство плавающей точки (рисунок 6.11) реализует арифметику с одинарной и двойной точностью в стандарте IEEE 754. Его устройство умножения используется также для выполнения операций целочисленного умножения. Устройства деления и вычисления квадратного корня работают с удвоенной частотой процессора. Арифметико-логическое устройство выполняет операции сложения, вычитания и преобразования форматов данных. Регистровый файл состоит из 28 64-битовых регистров, каждый из которых может использоваться как два 32-битовых регистра для выполнения операций с плавающей точкой одинарной точности. Регистровый файл имеет пять портов чтения и три порта записи, которые обеспечивают одновременное выполнение операций умножения, сложения и загрузки/записи.

Большинство улучшений производительности процессора связано с увеличением тактовой частоты до 100 МГц по сравнению с 66 МГц у его предшественника.

Рис. 6.11. Управление командами плавающей точки

Конвейер целочисленного устройства включает шесть ступеней: Чтение из кэша команд (IR), Чтение операндов (OR), Выполнение/Чтение из кэша данных (DR), Завершение чтения кэша данных (DRC), Запись в регистры (RW) и Запись в кэш данных (DW). На ступени ID выполняется выборка команд. Реализация механизма выдачи двух команд требует небольшого буфера предварительной выборки, который обеспечивает предварительную выборку команд за два такта до начала работы ступени IR. Во время выполнения на ступени OR все исполнительные устройства декодируют поля операндов в команде и начинают вычислять результат операции. На ступени DR целочисленное устройство завершает свою работу. Кроме того, кэш-память данных выполняет чтение, но данные не поступают до момента завершения работы ступени DRC. Результаты операций сложения (ADD) и умножения (MULTIPLY) также становятся достоверными в конце ступени DRC. Запись в универсальные регистры и регистры плавающей точки производится на ступени RW. Запись в кэш данных командами записи (STORE) требует двух тактов. Наиболее раннее двухтактное окно команды STORE возникает на ступенях RW и DW. Однако это окно может сдвигаться, поскольку записи в кэш данных происходят только когда появляется следующая команда записи. Операции деления и вычисления квадратного корня для чисел с плавающей точкой заканчиваются на много тактов позже ступени DW.

Конвейер проектировался с целью максимального увеличения времени, необходимого для выполнения чтения внешних кристаллов SRAM кэш-памяти данных. Это позволяет максимизировать частоту процессора при заданной скорости SRAM. Все команды загрузки (LOAD) выполняются за один такт и требуют только одного такта полосы пропускания кэш-памяти данных. Поскольку кэши команд и данных размещены на разных шинах, в конвейере отсутствуют какие-либо потери, связанные с конфликтами по обращениям в кэш данных и кэш команд.

Процессор может в каждом такте выдавать на выполнение одну целочисленную команду и одну команду плавающей точки. Полоса пропускания кэша команд достаточна для поддержания непрерывной выдачи двух команд в каждом такте. Отсутствуют какие-либо ограничения по выравниванию или порядку следования пары команд, которые выполняются вместе. Кроме того, отсутствуют потери тактов, связанных с переключением с выполнения двух команд на выполнение одной команды. Специальное внимание было уделено тому, чтобы выдача двух команд в одном такте не приводила к ограничению тактовой частоты. Чтобы добиться этого, в кэше команд был реализован специально предназначенный для этого заранее декодируемый бит, чтобы отделить команды целочисленного устройства от команд устройства плавающей точки. Этот бит предварительного декодирования команд минимизирует время, необходимое для правильного разделения команд.

Страницы: 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15